# **Advanced Toy Controller**

# W55VA91

# **Design Guide**

# Ver.A4

### **Special Characteristics**

- Powerful ARM926EJ-S core max 200MHz with fully 16/32 RISC architecture.

- High-performance 2D Graphic Engine performs high-speed 3D-like graphic function.

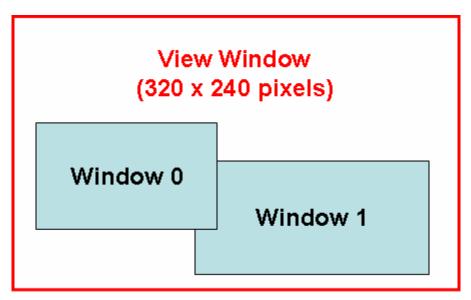

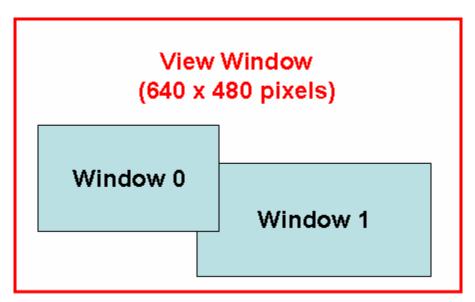

- GPU resolution support VGA and QVGA modes.

- Cost-effective on-chip JTAG interface debug solution.

- Built-in maximal 24KByte high-speed SRAM for graphics processing.

- Supports up to 64MB\* 2 banks external SDRAM.

- 2-channel GDMA for general data transfer without CPU intervention.

- UART serial bus communication support 16-byte receive buffer.

- Built-in one independent 26-bit Timer, and 4 16-bit PWM Timer.

- GPIO support 3 ports 16-bit programmable IOs.

- Interrupt controller support programmable priority for all interrupt sources

- Vectored interrupt mode minimize interrupt latency.

- 4 Power modes: Normal, Slow, Idle, and Stop mode.

- GPU support special 2D effects, rotation & scaling, scrolling, fad-in, fad-out, a-blending.

- Support 4 Tiled or Bitmap BGs (BG0~BG3) and 1 Video\_in BG4.

- Video\_in support buffer mode allowable of play-on-TV interactive game.

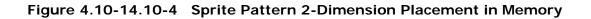

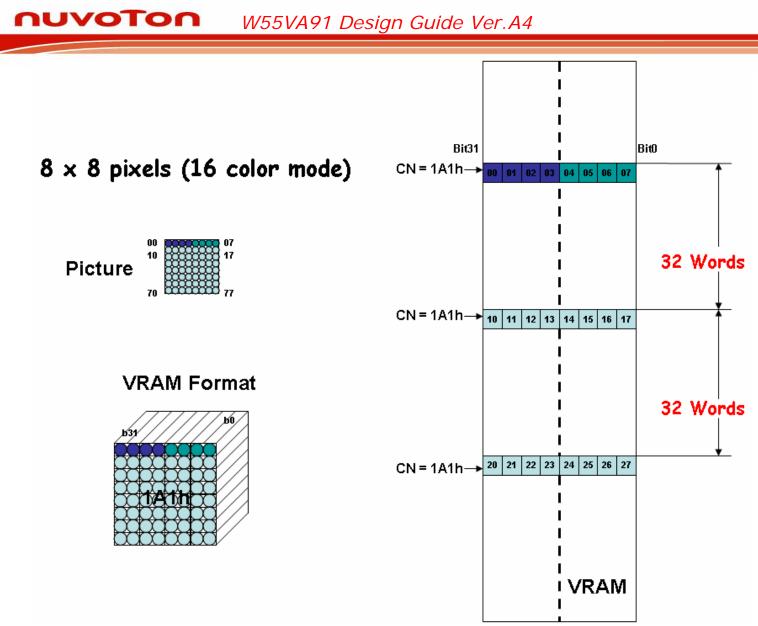

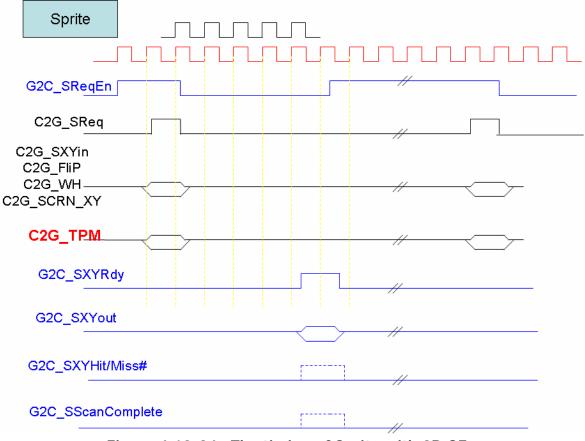

- Sprites support 8\*8~64\*64 size; 16/256 color mode.

- Sprites support cell mode and bitmap mode.

- Video\_out support NTSC or PAL mode.

- CRT light-pen interface for shooting game.

- Support 16-bit watch dog timer (WDT).

- 2-channel DAC, support stereo audio output.

- 2 rectangle window + sprite window function to aid graphic effect.

- Minimum 24 sprites per raster line.

- 1 TVDAC for TV encoder output.

- Support 8-channel 10-bit multiplexed ADC.

- Hardware JPEG codec engin.

- Hardware SD card and NAND-type Flash Controller.

- USB1.1 Host Controller with 2 hub ports.

- USB1.1 Device Controller supports for Full speed 12Mbps.

### - Table of Contents -

| 1 |            | Description                                       |   |

|---|------------|---------------------------------------------------|---|

| 2 | Features.  |                                                   | 5 |

| 3 | Block Dia  | gram                                              | 8 |

| 4 | Functiona  | I Description                                     | 9 |

| 1 | 4.1        | ARM926EJ-S CPU Core                               | 9 |

| 4 | 4.2        | System Manager10                                  | 0 |

| 4 | 4.3        | External Bus Interface                            | 2 |

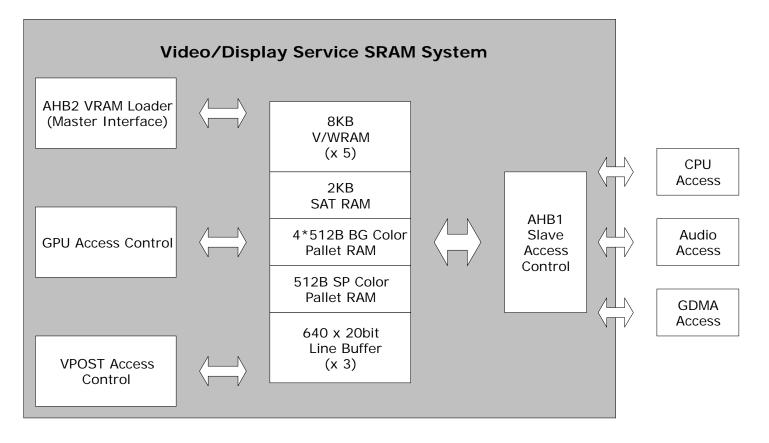

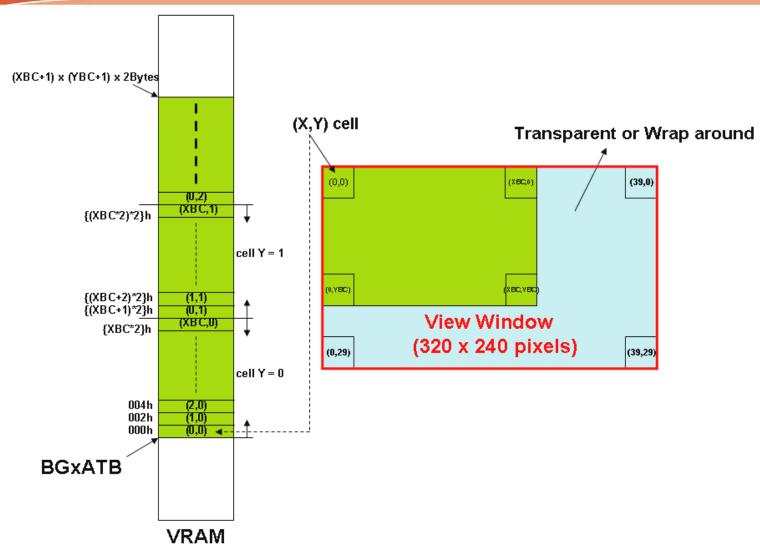

| 4 | 4.4        | Video/Display Service SRAM System (VRAM)          | 8 |

| 4 | 4.5        | Advanced Interrupt Controller                     | 2 |

| 4 |            | Audio Processing Unit                             |   |

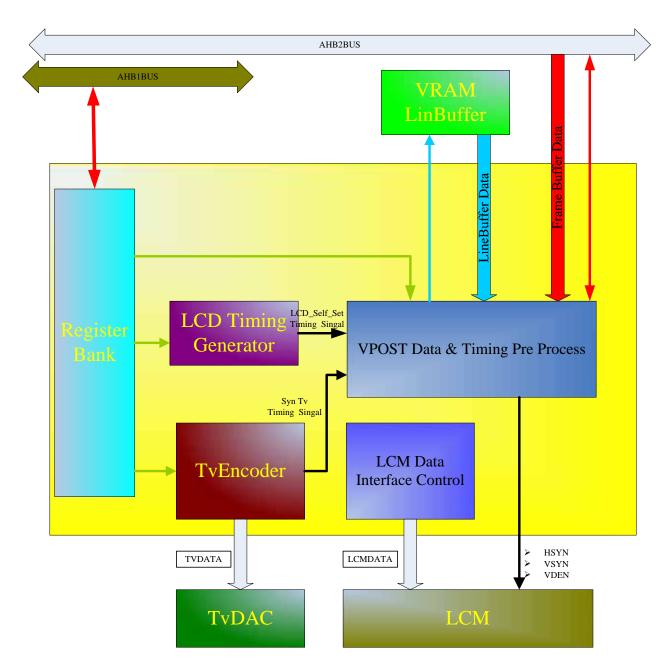

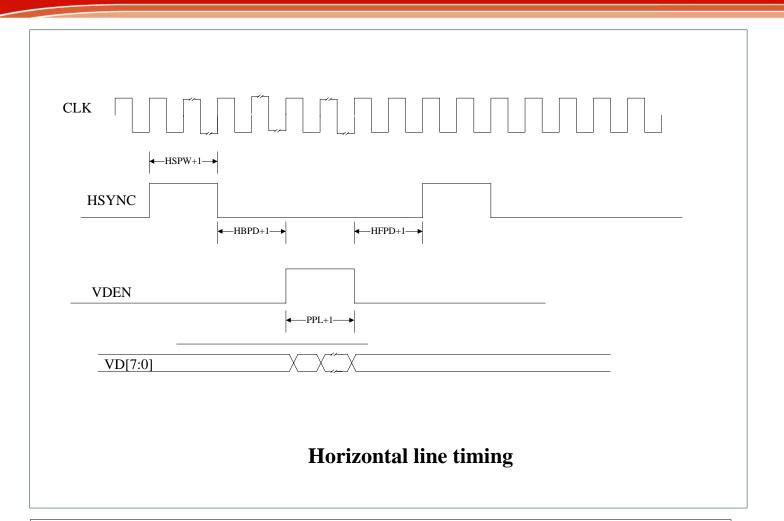

| 4 | 4.7        | Display Interface Controller (VPOST)110           | 6 |

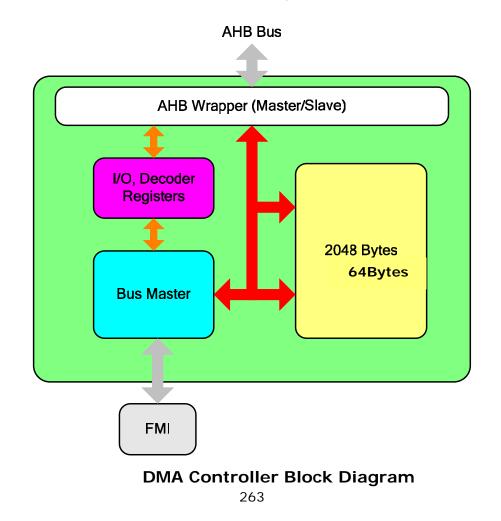

| 4 | 4.8        | General DMA Controller                            | 2 |

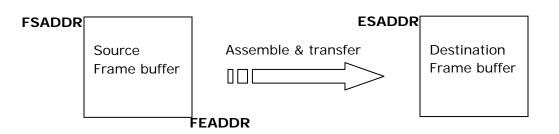

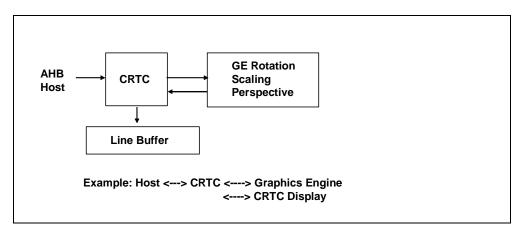

| 4 | 4.9        | 2-D Graphic Engine                                | 1 |

| 4 | 4.10       | Graphic Processing Unit                           | 5 |

| 4 | 4.11       | Flash Memory Interface Controller (FMI)           | 8 |

| 4 | 4.12       | FMI DMA Controller                                | 3 |

| 4 | 4.13       | Video-In Processor                                | 8 |

| 4 | 4.14       | JPEG Codec                                        | 0 |

| 4 | 4.15       | Analog to Digital Converter                       | 7 |

| 4 | 4.16       | General Purpose I/O                               | 0 |

| 4 | 4.17       | USB Device Controller                             | 8 |

| 4 | 4.18       | USB Host Controller                               | 1 |

| 4 | 4.19       | PWM-Timer                                         | 2 |

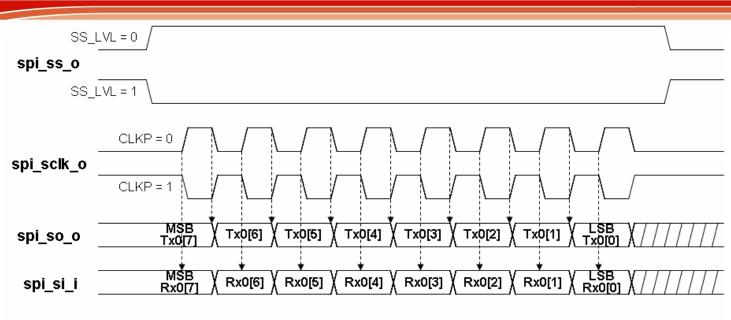

| 4 | 4.20       | SPIO Serial Interface Controller (Master/Slave)41 | 1 |

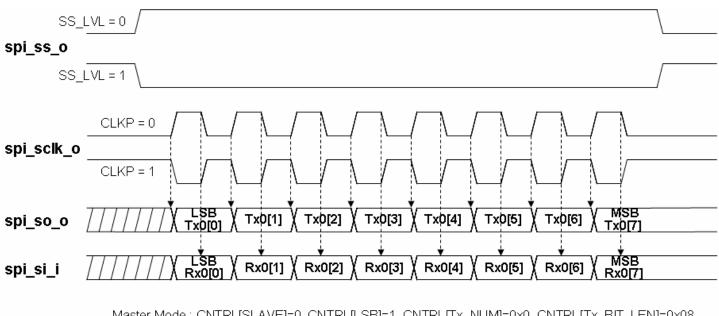

| 4 | 4.21       | SPI1 Serial Interface Controller (Master Only)42  | 1 |

| 4 | 4.22       | Timer and Watchdog Timer                          | 9 |

| 4 | 4.23       | RTC                                               | 5 |

| 4 | 4.24       | UART                                              | 3 |

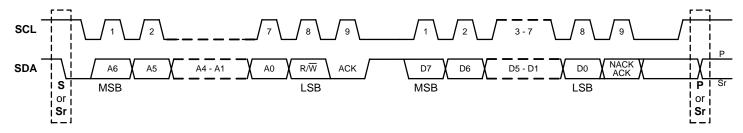

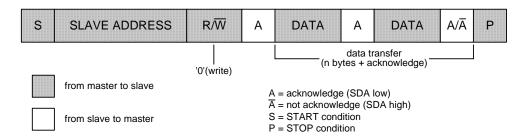

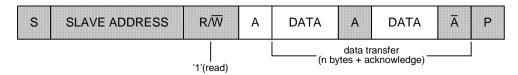

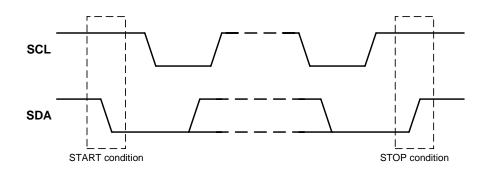

| 4 | 4.25       | I2C interface                                     | 5 |

| 5 | Electrical | Specifications                                    | 7 |

| į | 5.1        | Absolute Maximum Ratings                          | 7 |

| Į | 5.2        | DC Specifications                                 | 7 |

| į | 5.3        | AC Specifications                                 | 8 |

| Į | 5.4        | Audio DAC Characteristic                          | 0 |

| Į | 5.5        | TV DAC Characteristic                             | 0 |

| ĺ |            | ADC Characteristic                                |   |

| ĺ |            | Low voltage detect Characteristic                 |   |

|   |            | Low voltage reset Characteristic                  |   |

|   |            | am47                                              |   |

| 7 | •          | iption                                            |   |

| 8 |            | t Revision History                                |   |

# **1** General Description

The W55VA91 is an "edutainment" TV game controller based on the 16/32-bit ARM RISC-like, cost-effective, high-performance processor. It features a built-in TV encoder for convenient TV display, a high-quality stereo audio DAC output, a large set of peripherals, such as a USB Host/device, an 8-Channel ADC, SD/SDIO Card I/F, SPI I/F, and a complete set of system functions minimizing the number of external components. The highly integrated features can be combined with other auxiliary components to form a completed system platform that let TV game producers easily implement their cost-effective, competitive, and powerful TV game solutions.

The following integrated on-chip functions are described in details in this document.

- Embedded 20K bytes Boot ROM

- External Bus Interface Controller

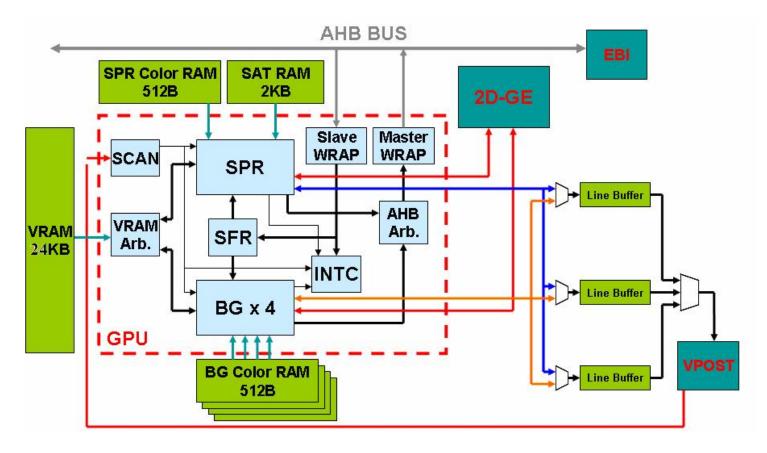

- Graphic Processing Unit (GPU)

- 2-D Graphic Engine

- 1-Channel TV Encoder/DAC

- LCD controller supporting TFT/STN LCD modules

- MP3 class 16-bit 2-Channel Audio DAC

- 8-Channel 10-bit ADC

- GDMA

- SD/SDIO Card interface

- UART interface

- USB Host/ Device interface

- JPEG Codec

- Video In, CMOS interface

- SPI interface

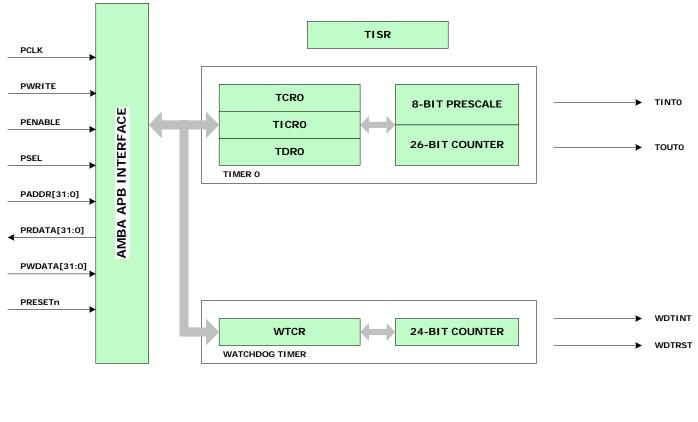

- Timers and Watchdog Timer

- 24 Programmable I/O Ports

- Advanced Interrupt Controller

- 2-Channel PWM with capture function

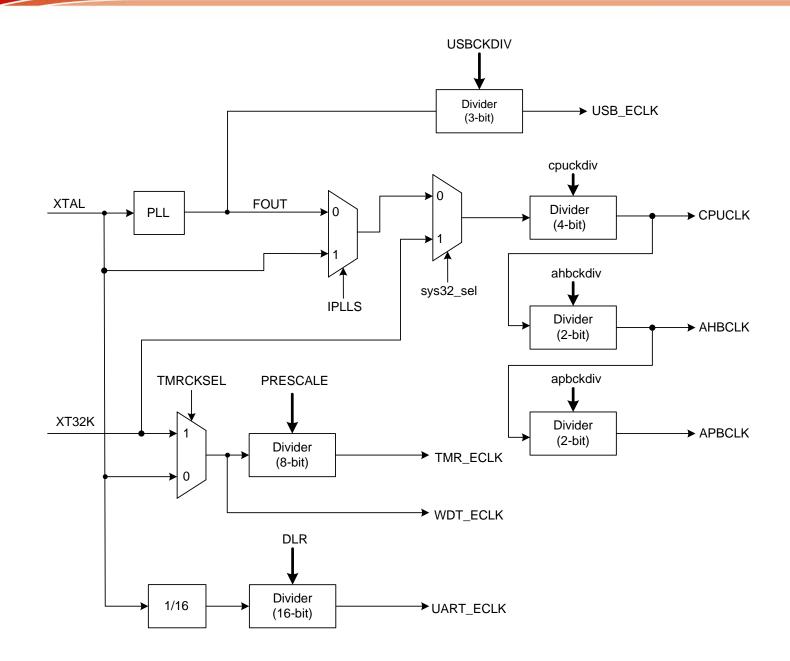

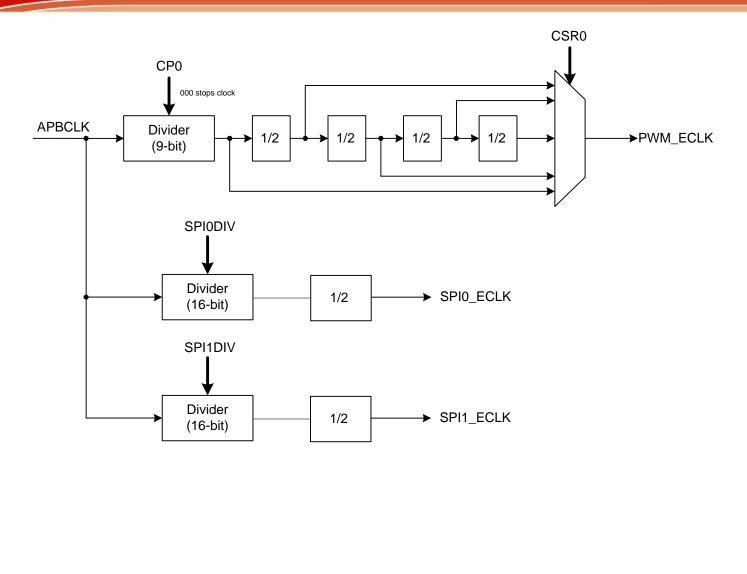

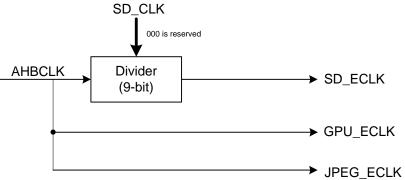

- System Manager with PLL System Clock Synthesizer

- Real-time clock source

- Low-voltage Detector and Low-voltage Reset

# 2 Features

#### Architecture

- Fully 16/32-bit RISC architecture

- Little-endian mode supported

- Efficient and powerful ARM926EJ-S core

- Cost-effective JTAG-based debug solution

#### External Bus Interface

- 8/16/32-bit external bus support for ROM/SRAM, flash memory, SDRAM and external I/Os

- Support for SDRAM

- Programmable access cycle (0-7 wait cycle)

- Four-word depth write buffer for SDRAM write data

- Cost-effective memory-to-peripheral DMA interface

#### Graphic Processing Unit (GPU)

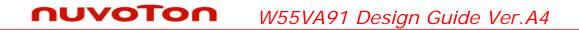

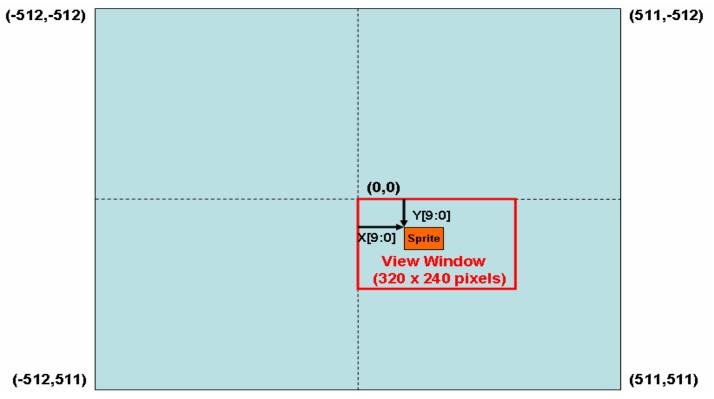

- Provide two Resolutions: QVGA (320x240) and VGA (640x480).

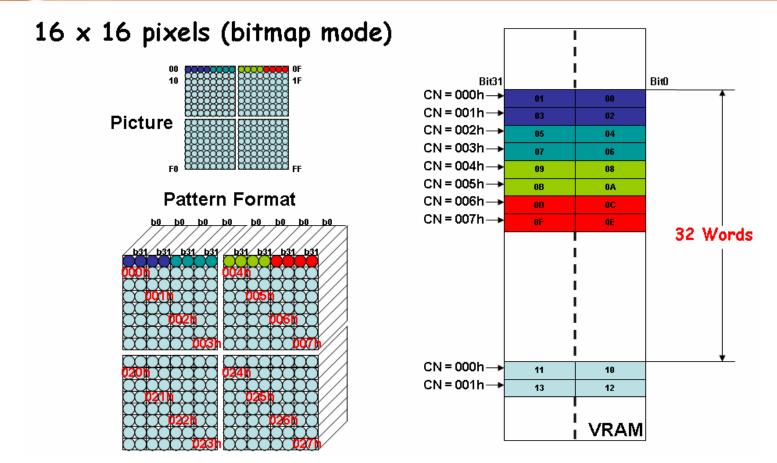

- Background/ Sprite provide both cell mode and bitmap mode.

- Programmable priority for sprites.

- Number of sprite per line: including rotation/scaling, worse case is 24 for 8\*8 sprites.

- HV-Flip + Alpha blending + Fad-in + Fad-out + scrolling.

- Scrolling: HV scrolling, with programmable scrolling rate.

- Alpha blending: 16 levels resolution.

- Fad-in & Fad-out: 16 level resolution.

- Five Color Pallet RAMs supported: for sprites/ 4x backgrounds color pallets respectively.

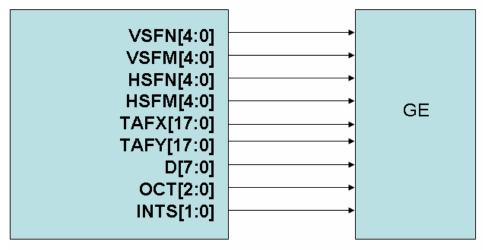

#### 2D Graphic Engine

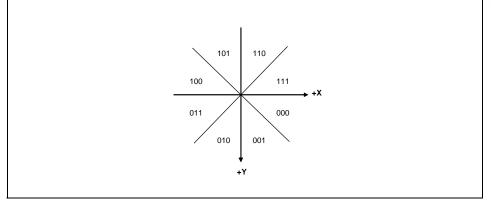

- 6 sprites rotation and scaling per-line supported.

- 1 background rotation and scaling supported.

- Perspective projection for background.

#### Video-In Processor

- Direct connect to CCD or CMOS image sensor with CCIR601.

- Support the interface of TV-decoder.

- Input/ Output data format, YUV422, RGB555.

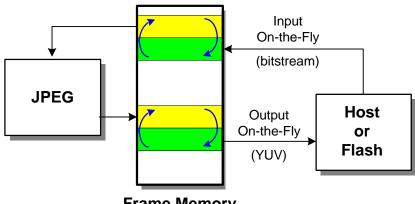

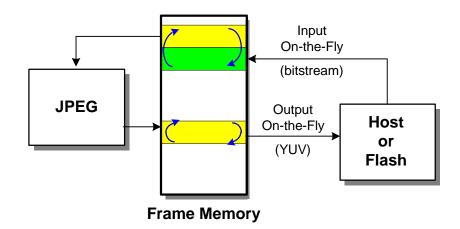

#### JPEG encoder/ decoder

Planar format:

- Support to encode interleaved YCbCr 4:2:2/4:2:0 and gray-level (Y only) format image

- Support to decode interleaved YCbCr 4:4:4/4:2:2/4:2:0/4:1:1 and gray-level (Y only) format image

- Support to decode YCbCr 4:2:2 transpose format

Packet format:

- Support to encode interleaved YUYV format input image, output bitstream 4:2:2 and 4:2:0 format

- Support to decode interleaved YCbCr 4:4:4/4:2:2/4:2:0 format image

- Support decoded output image RGB555 format (ORDER= 1).

#### USB Host/ Device interface

- Provide 2 Host with both low speed and full speed

- Provide 1 Device with full speed

#### DMA Controller

- 2-channel General DMA for memory-to-memory data transfers without CPU intervention

- Initiated by software

- Increments or decrements a source or destination address in 8-bit, 16-bit or 32-bit data transfers

- 8-data burst mode

#### UART

- One UART (serial I/O) block with interrupt-based operation

- Support for 5-bit, 6-bit, 7-bit or 8-bit serial data transmit and receive

- Programmable baud rates

- 1,  $\frac{1}{2}$  or 2 stop bits

- Odd or even parity

- Break generation and detection

- Parity, overrun and framing error detection

- X16 clock mode

#### Timers / Watch-Dog Timer

- Four programmable 16-bit PWM timers with two 8-bit pre-scalars

- One programmable 26-bit Watchdog timer

- One-short mode or period mode operation

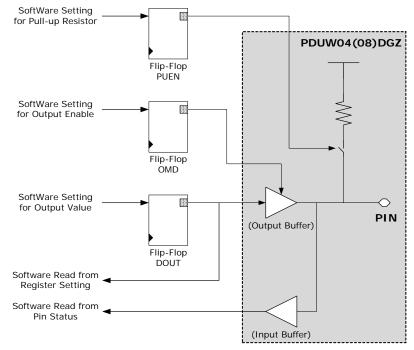

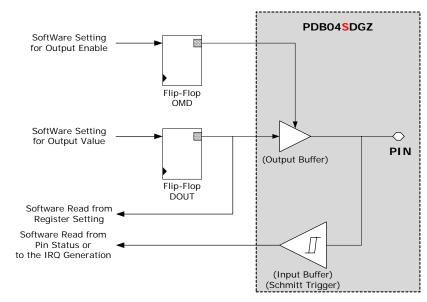

#### Programmable I/Os

- 32~ programmable I/O ports

- Pins individually configurable to input, output or I/O mode for dedicated signals

- I/O ports are configurable for Multiple functions

#### Advanced Interrupt Controller

- 31 interrupt sources, including 4 external interrupt sources

- Programmable normal or fast interrupt mode (IRQ, FIQ)

- Programmable as either edge-triggered or level-sensitive for 4 external interrupt sources

- Programmable as either low-active or high-active for 4 external interrupt sources

- Priority methodology is encoded to allow for interrupt daisy-chaining

- Automatically mask out the lower priority interrupt during interrupt nesting

- Automatically clear the interrupt flag when the interrupt source is programmed to be edge-triggered

#### Audio DAC

- Stereo 16-bit MP3 level output

- Headphone driver embedded

#### Display Interface

- Sync-Type TFT LCD Controller

- Sync-Type Color STN LCD Controller

- MPU-Type LCD Controller

- Embedded TV Encoder Support NTSC and PAL modes

- Support to merge YUV422 and RGB555 system.

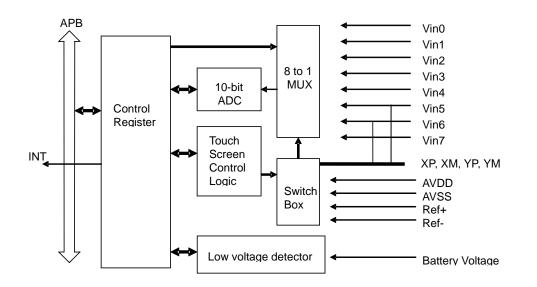

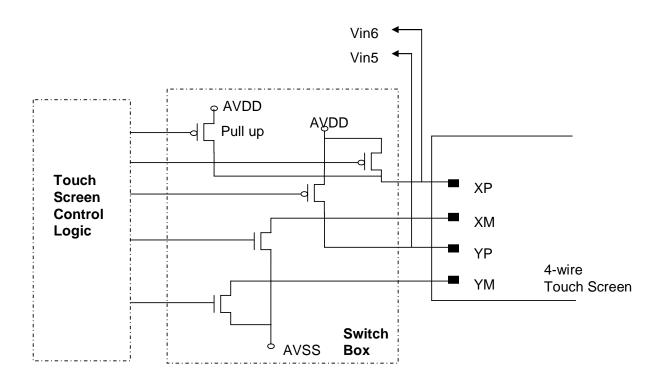

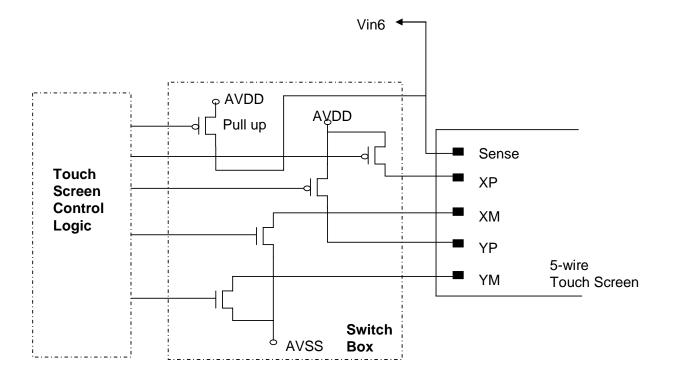

#### Analog to Digital Converter and Touch Screen

- Maximum conversion rate: 250K samples per second

- 8 channel analog input

- Power supply voltage: 3.3V

- Analog input voltage range: 0 3.3 volts

- Touch screen semi-auto/auto conversion modes supported

- Support 4-wire and 5-wire Touch Screen

- Waiting for trigger mode supports

- Standby mode supports

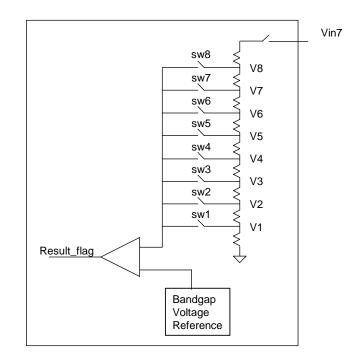

- 8-level voltage detector

#### PLL

• Transfer the input oscillator clock (6~15MHz) into higher clock rate for system operation usage.

#### Real Time Clock (RTC) Source

- Independent power supply from chip to save power consumption.

- 32.768K Hz Crystal oscillation circuit

- Provide hardware alarm function

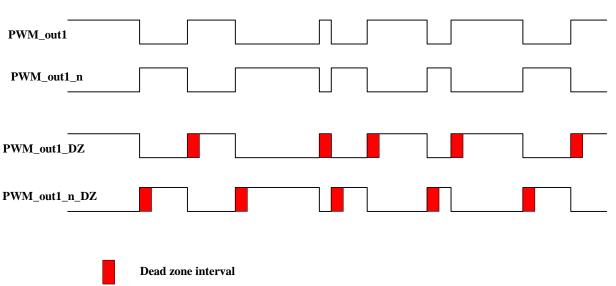

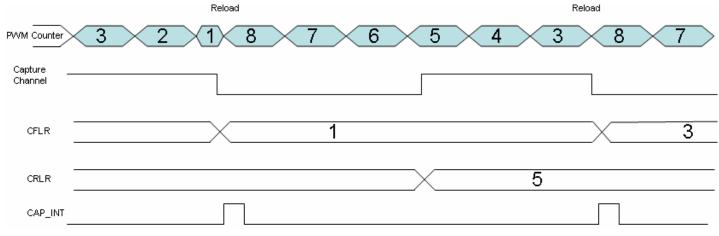

#### 4-Channel PWM

- Four 16-bit timers

- Programmable duty control of output waveform (PWM)

- Auto reload mode or one-shot pulse mode

- Dead-zone generator

- Capture function.

#### Power management

- Programmable clock enables for individual peripheral

- IDLE mode to halt ARM Core and keep peripheral working

- Power-Down mode to stop all clocks including external crystal oscillator.

- Exit IDLE/Power-Down by interrupts

#### **Operation Voltage Range**

- 2.7 ~ 3.6 V for IO Buffer

- 1.62 ~ 1.98 V for Core Logic

#### **Operation Temperature Range**

• 0 ~ 70 Degree C

#### ESD 2KV

#### **Operating Frequency**

- CPU Core: Up to 200 MHz

- System: Up to 133 MHz

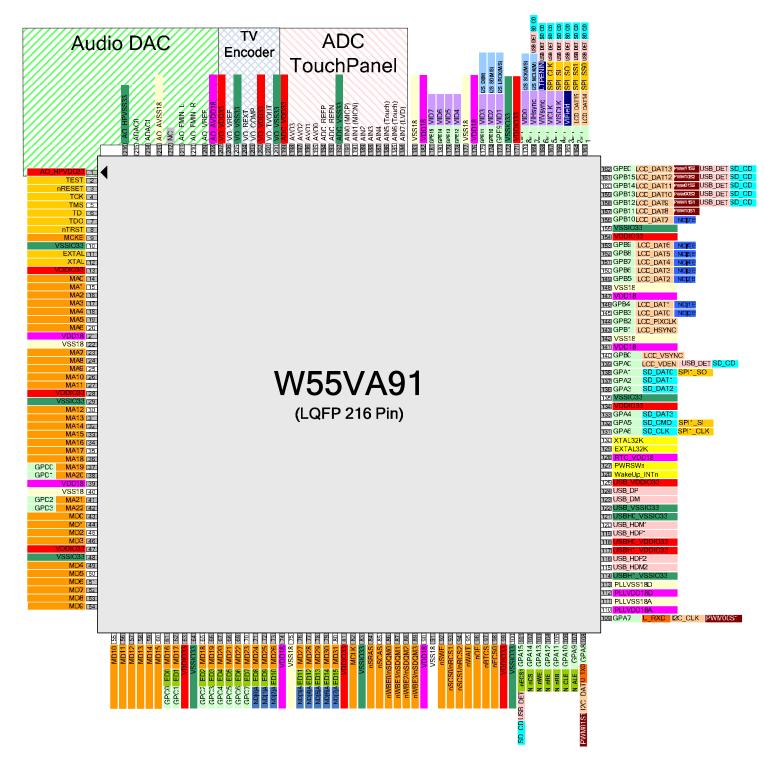

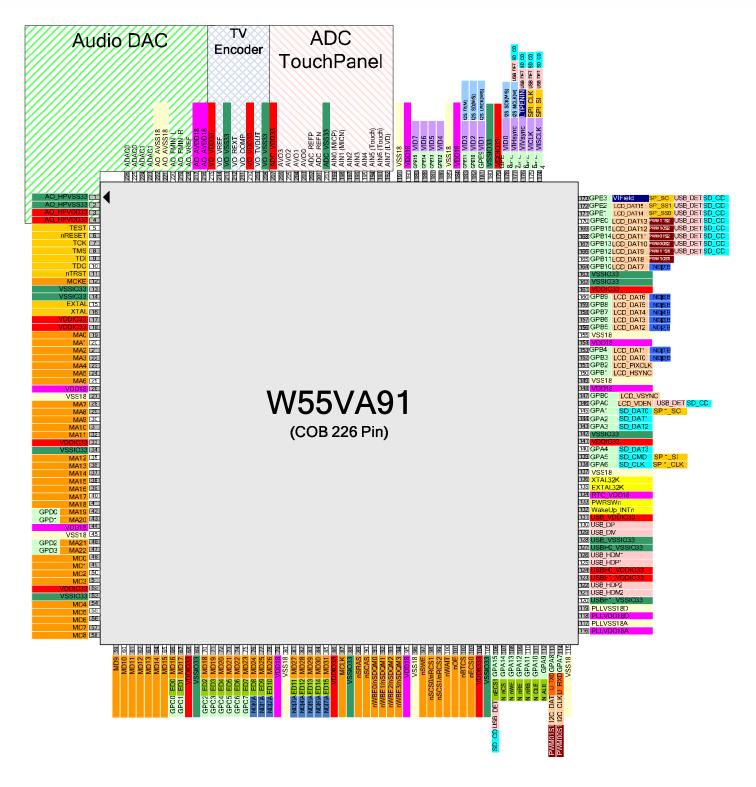

#### Package Type

• 216-pin LQFP

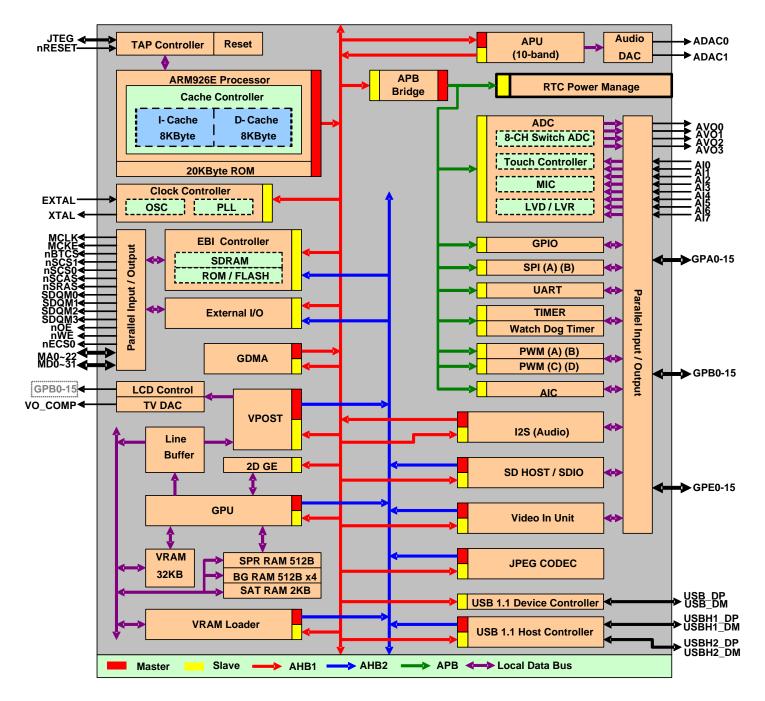

**3 Block Diagram**

Figure 3–1 W55VA91 Block and Bus Architecture Diagram

# **4 Functional Description**

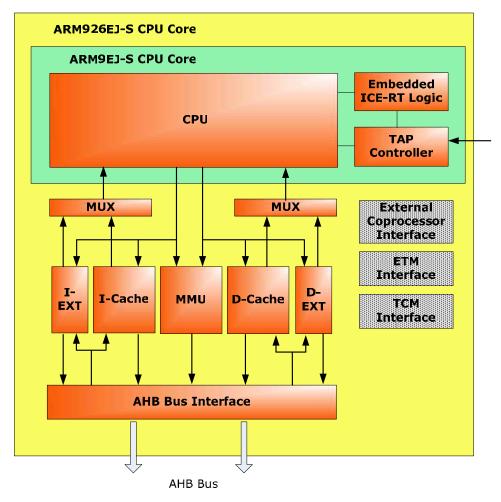

## 4.1 ARM926EJ-S CPU Core

The ARM926EJ-S CPU core is a member of the ARM9 family of general-purpose microprocessors. The ARM926EJ-S CPU core is targeted at multi-tasking applications where full memory management, high performance, low die size, and low power are all important. The ARM926EJ-S CPU core supports the 32-bit ARM and 16-bit Thumb instruction sets, enabling the user to trade off between high performance and high code density. The ARM926EJ-S processor has a Harvard cached architecture and provides a complete high-performance processor subsystem, including:

- An ARM926EJ-S integer core

- A Memory Management Unit (MMU)

- Separate instruction and data AMBA AHB bus interfaces

Figure 4.1-1 ARM926EJ-S CPU Core Block Diagrm

## 4.2 System Manager

### 4.2.1 Overview

The W55VA91 System Manager has the following functions.

- System memory map

- The width of external memory address

- Data bus connection with external memory

- Product identifier register

- Bus arbitration

- PLL module

- Clock divider setting for some special functions needing clocks other than system bus clock

- Clock select, enable and power saving control register

- Power-On setting reading and alternating

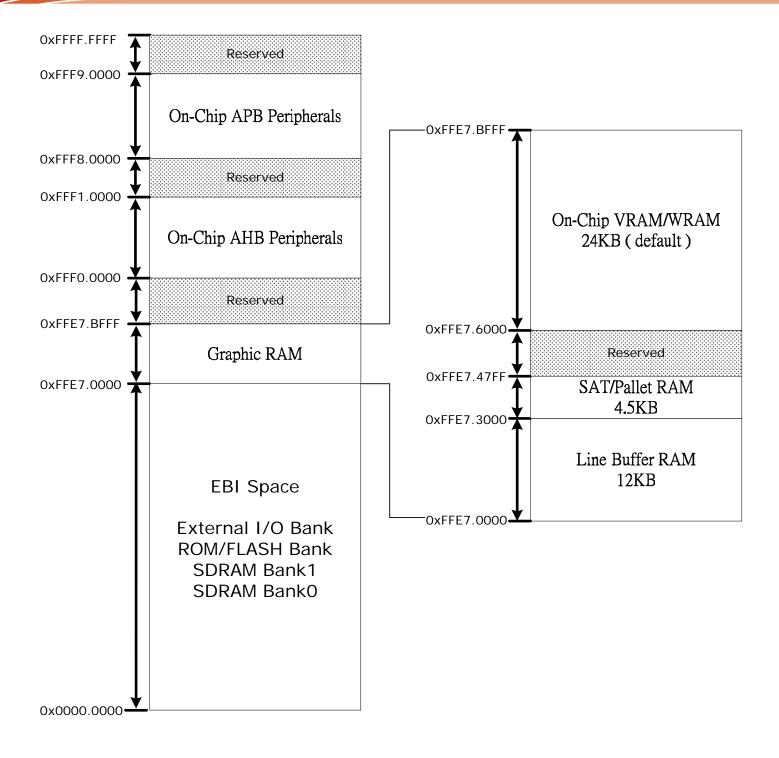

#### 4.2.2 System Memory Map

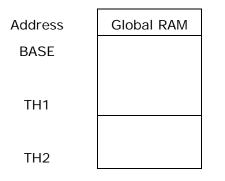

W55VA91 provides 2G bytes cacheable address space and the other 2G bytes are non-cacheable. The On-Chip Peripherals bank is on 1M bytes top of the space (0xFFF0.0000 – 0xFFFF.FFFF) and the On-Chip RAM bank's start address is 0xFFE0.0000, the other banks can be located anywhere (cacheable space: 0x0~0x7FDF.FFFF if Cache ON; non-cacheable space: 0x8000.0000~0xFFDF.FFFF).

The size and location of each bank is determined by the register settings for "current bank base address pointer" and "current bank size". Please note that when setting the bank control registers, the address boundaries of consecutive banks must not overlap each other.

Except On-Chip Peripherals and On-Chip RAM, the start address of each memory bank is not fixed. You can use bank control registers to assign a specific bank start address by setting the bank's base pointer (13 bits). The address resolution is 256K bytes. The start address of a bank is defined as "base pointer << 18" and the size of this bank is "current bank size."

In the event of an access request to an address outside any programmed bank size, an abort signal is generated. The maximum accessible memory size of each external IO bank is 16M bytes, and 64M bytes on SDRAM banks.

Figure 4.2-1 Figure System Memory Map

| Base Address    | Description                                                     |

|-----------------|-----------------------------------------------------------------|

| AHB Peripherals |                                                                 |

| 0xFFF0_0000     | Product Identifier Register (PDID)                              |

| 0xFFF0_0004     | Power-On Configurations from EBI Address (PWRON)                |

| 0xFFF0_0008     | Arbitration Control Register (ARBCON)                           |

| OxFFF0_000C     | PLL Control Register (PLLCON)                                   |

| 0xFFF0_0010     | Clock source Management for peripherals                         |

| 0xFFF0_0014     | Clock Source Select and Division setting (CLKSEL)               |

| 0xFFF0_0018     | Reset Control Register (RSTCON)                                 |

| 0xFFF0_001C     | Pins Multifunction Control Register (PINFUN)                    |

| 0xFFF0_0020     | Crystal on/off status Control Register (XTLCON)                 |

| 0xFFF0_0024     | IRQ Wakeup Control Register (IRQWAKEUPCON)                      |

| 0xFFF0_0028     | IRQ Wakeup Flag Regitser (IRQWAKEFLAG)                          |

| 0xFFF0_002C     | Power Manager Control Register (PMCON)                          |

| 0xFFF0_0030     | GPA/GPB I/O Cells Dual-Driving Select Control Register (GPABDS) |

| 0xFFF0_0034     | GPC/GPD I/O Cells Dual-Driving Select Control Register (GPCDDS) |

| 0xFFF0_0038     | EBI I/O Cells Triple-Driving Select Control Register(EBIDDS)    |

| 0xFFF0_003C     | System clock divider (SYSDIV)                                   |

| 0xFFF0_0040     | Internal Boot ROM Base (IBTBAS)                                 |

| 0xFFF0_0044     | Working(or Video) RAM mapping to start address 0x0 (WPAM0)      |

| 0xFFF0_0048     | Pins Multifunction 2 Control Register (PINFUN2)                 |

| 0xFFF0_0050     | CPU RAM BIST Control Register (RAMBIST)                         |

| 0xFFF0_0054     | CPU RAM BIST Control Register(RAMSTAT)                          |

| 0xFFF0_1000     | EBI Control Register (EBICON) Control Registers                 |

| 0xFFF0_1004     | ROM/FLASH Boot Memory (ROMCON) Control Registers                |

| 0xFFF0_1010     | SDRAM bank 0 – 1 Control Registers                              |

| 0xFFF0_1020     | External I/O Control Registers                                  |

| 0xFFF0_3000     | GDMA 0 – 1 Control Registers                                    |

| 0xFFF0_4000     | GPU Control Registers                                           |

| 0xFFF0_5000     | 2-D Graphic Engine Control Registers                            |

| 0xFFF0_6000     | Display Interface (VPOST) Control Registers                     |

| 0xFFF0_7000     | Video-in Controller Control Registers                           |

| 0xFFF0_8000     | Audio IIS Controller (hidden)                                   |

| 0xFFF0_9000     | SD Card Host Control Registers                                  |

| 0xFFF0_A000     | Audio Processing Unit Control Registers                         |

| 0xFFF0_B000     | VRAM/PRAM Service System Registers                              |

| 0xFFF0_C000     | USB Device Registers                                            |

| 0xFFF0_D000     | USB Host registers                                              |

| 0xFFF0_E000     | JPEG control registers                                          |

| APB Peripherals |                                                                 |

| 0xFFF8_0000     | UART 0 (Tx, RX for console)                                     |

| 0xFFF8_1000     | Timer 0, WDOG Timer                                             |

| 0xFFF8_2000     | PWM/Timer 0 – 1                                                 |

| 0xFFF8_3000     | Advanced Interrupt Controller                                   |

| 0xFFF8_4000 | GPIO                              |

|-------------|-----------------------------------|

| 0xFFF8_5000 | ADC Control Registers             |

| 0xFFF8_6000 | SPI Interface Control Registers   |

| 0xFFF8_7000 | RTC Interface Control Registers   |

| 0xFFF8_8000 | SPI 1 Interface Control Registers |

| 0xFFF8_9000 | I2C Interface Control Registers   |

#### Table 4.2-1 On-Chip Peripherals Memory Map

The following table lists the base address of Working/Video RAM, Pallet RAM, SAT RAM, and Display Line Buffer RAM.

| Base Address | Description                                      |

|--------------|--------------------------------------------------|

| 0xFFE7_0000  | Display Line Buffer 0 Base (640 Words effective) |

| 0xFFE7_1000  | Display Line Buffer 1 Base (640 Words effective) |

| 0xFFE7_2000  | Display Line Buffer 2 Base (640 Words effective) |

| 0xFFE7_3000  | Background Color Pallet0 RAM Base (512 Bytes)    |

| 0xFFE7_3200  | Background Color Pallet1 RAM Base (512 Bytes)    |

| 0xFFE7_3400  | Background Color Pallet2 RAM Base (512 Bytes)    |

| 0xFFE7_3600  | Background Color Pallet3 RAM Base (512 Bytes)    |

| 0xFFE7_3800  | Sprite Color Pallet RAM Base (512 Bytes)         |

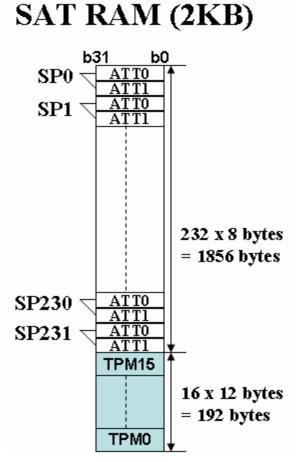

| 0xFFE7_4000  | SAT RAM Base (2K Bytes)                          |

| 0xFFE7_6000  | Working/Video RAM Bank0 Base (8K Bytes)          |

| 0xFFE7_8000  | Working/Video RAM Bank1 Base (8K Bytes)          |

| 0xFFE7_A000  | Working/Video RAM Bank2 Base (8K Bytes)          |

Table 4.2-2 On-Chip RAM Base Address Table

### 4.2.3 Address Bus Generation

The W55VA91 address bus generation is depended on the required data bus width of each memory bank. The data bus width is determined by **DBWD** bits in each bank's control register.

| The maximum | agaaadibla | momory                                  | cize of | aaah | outornal  | 10  | honkin  | ONIL   | + ~ ~ |

|-------------|------------|-----------------------------------------|---------|------|-----------|-----|---------|--------|-------|

| пе пахіпип  | accessiole | memory                                  | SIZE OF | each | external  | 1() | DADKIN  |        | Ies – |

|             | 4000001010 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 0120 01 | ouon | ontorriar |     | Num III | $\sim$ |       |

| Data Bus | Exte       | ernal Address Pi | Maximum Accessible |              |

|----------|------------|------------------|--------------------|--------------|

| Width    | A [19:0]   | A20              | A21                | Memory Size  |

| 0 bit    | A19 – A0   | A20              | A21                |              |

| 8-bit    | (Internal) | (Internal)       | (Internal)         | 4M bytes     |

| 1( bit   | A20 – A1   | A21              | A22                | 8M bytes     |

| 16-bit   | (Internal) | (Internal)       | (Internal)         | (half-words) |

| 32-bit   | A21 – A2   | A22              | A23                | 16M bytes    |

| 32-DII   | (Internal) | (Internal)       | (Internal)         | (words)      |

Table 4.2-3

Address Bus Generation Guidelines

### 4.2.4 Data Bus Connection with External Memory

#### 4.2.4.1 Memory Format – Little Endian

The memory format for the external memory data bus connection is little endian. For the little endian format, the lowest addressed byte in a word is considered the least significant byte of the word and the highest addressed bye is the most significant. So the byte at address 0 of the memory system connects to data lines 7 through 0.

For a word aligned address A, reference **Table 4.2-4**, shows how the word at address A, the half-word at addresses A and A+2, and the bytes at addresses A, A+1, A+2, and A+3 map on to each other.

| 31 | 3                                       | 0 29 | 9 2 | 8 | 27 | 26 | 25 | 24                                  | 23 | 22 | 21 | 20 | 19 | 18  | 17   | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|-----------------------------------------|------|-----|---|----|----|----|-------------------------------------|----|----|----|----|----|-----|------|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    | Word at address A                       |      |     |   |    |    |    |                                     |    |    |    |    |    |     |      |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|    | Half-word at address A+2                |      |     |   |    |    |    | Half-word at address A              |    |    |    |    |    |     |      |    |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| B  | Byte at address A+3 Byte at address A+2 |      |     |   |    |    |    | 2 Byte at address A+1 Byte at addre |    |    |    |    |    | res | ss A | 4  |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

#### Table 4.2-4 Little-endian addresses of bytes and half-words within words

#### 4.2.4.2 Connection of External Memory with Various Data Width

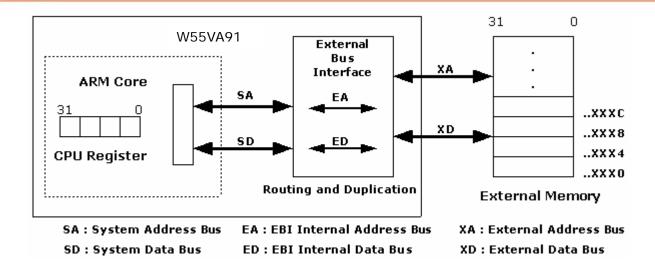

The system diagram for W55VA91 connecting with the external memory is shown in

| Base Address | Description                                      |

|--------------|--------------------------------------------------|

| 0xFFE7_0000  | Display Line Buffer 0 Base (640 Words effective) |

| 0xFFE7_1000  | Display Line Buffer 1 Base (640 Words effective) |

| 0xFFE7_2000  | Display Line Buffer 2 Base (640 Words effective) |

| 0xFFE7_3000  | Background Color Pallet0 RAM Base (512 Bytes)    |

| 0xFFE7_3200  | Background Color Pallet1 RAM Base (512 Bytes)    |

| 0xFFE7_3400  | Background Color Pallet2 RAM Base (512 Bytes)    |

| 0xFFE7_3600  | Background Color Pallet3 RAM Base (512 Bytes)    |

| 0xFFE7_3800  | Sprite Color Pallet RAM Base (512 Bytes)         |

| 0xFFE7_4000  | SAT RAM Base (2K Bytes)                          |

| 0xFFE7_6000  | Working/Video RAM Bank0 Base (8K Bytes)          |

| 0xFFE7_8000  | Working/Video RAM Bank1 Base (8K Bytes)          |

| 0xFFE7_A000  | Working/Video RAM Bank2 Base (8K Bytes)          |

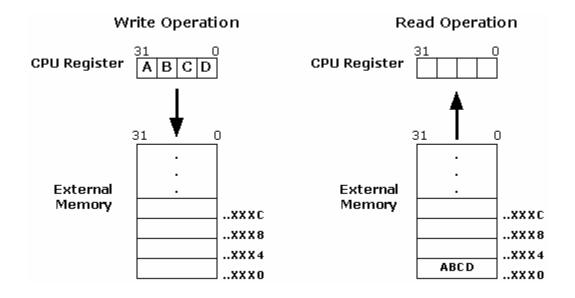

Table 4.2-2 and **Figure 4.2-3**. Below tables (through **Table 4.2-5** and **Table 4.2-6**) show the program/data path between CPU register and the external memory using little endian and word/half-word/byte access.

Figure 4.2-2 Address/Data bus connection with external memory

Using little-endian and word access, Program/Data path between register and external memory WA = Address whose LSB is 0,4,8,C X = Don't care nWBE [3-0] / SDQM [3-0] = A means active and U means inactive

| Access Operation |                             | Write Operation (C | PU Register 🗲 External Memory) |

|------------------|-----------------------------|--------------------|--------------------------------|

| XD Width         | Word                        | Half Word          | Byte                           |

| Bit Number       | <b>Bit Number</b> 31 0 31 0 |                    | 31 0                           |

| CPU Reg Data     | ABCD                        | ABCD               | ABCD                           |

| SA               | WA                          | WA                 | WA                             |

| Bit Number       | 31 0                        | 31 0               | 31 0                           |

| SD               | ABCD                        | AB CD              | A B C D                        |

| Bit Number                 | 31 0 | 15 0      | 15 0      | 7 0       | 7 0       | 7 0       | 7 0       |

|----------------------------|------|-----------|-----------|-----------|-----------|-----------|-----------|

| ED                         | ABCD | CD        | AB        | D         | С         | В         | А         |

| ХА                         | WA   | WA        | WA+2      | WA        | WA+1      | WA+2      | WA+3      |

| nWBE [3-0] /<br>SDQM [3-0] | AAAA | ХХАА      | ХХАА      | ХХХА      | ХХХА      | ХХХА      | XXXA      |

| Bit Number                 | 31 0 | 15 0      | 15 0      | 7 0       | 7 0       | 7 0       | 7 0       |

| XD                         | ABCD | CD        | AB        | D         | С         | В         | А         |

| Bit Number                 | 31 0 | 15 0      | 15 0      | 7 0       | 7 0       | 7 0       | 7 0       |

| Ext. Mem Data              | ABCD | CD        | AB        | D         | С         | В         | А         |

| Timing Sequence            |      | 1st write | 2nd write | 1st write | 2nd write | 3rd write | 4th write |

Table 4.2-5 Word access write operation with Little Endian

| Access Operation            |              | Read          | Operation (Cl | PU Register 🗲   | External Mem    | nory)           |                 |  |  |

|-----------------------------|--------------|---------------|---------------|-----------------|-----------------|-----------------|-----------------|--|--|

| XD Width                    | Word         | Half          | Word          | Byte            |                 |                 |                 |  |  |

| Bit Number<br>CPU Reg Data  | 31 0<br>ABCD | 31<br>AB      | 0<br>CD       | 31 0<br>ABCD    |                 |                 |                 |  |  |

| SA                          | WA           | W             | /A            | WA              |                 |                 |                 |  |  |

| Bit Number<br>SD            | 31 0<br>ABCD | 31<br>AB      | 0<br>CD       | 31 0<br>A B C D |                 |                 |                 |  |  |

| Bit Number<br>ED            | 31 0<br>ABCD | 31 0<br>XX CD | 31 0<br>AB CD | 31 0<br>X X X D | 31 0<br>X X C D | 31 0<br>X B C D | 31 0<br>A B C D |  |  |

| ХА                          | WA           | WA            | WA+2          | WA              | WA+1            | WA+2            | WA+3            |  |  |

| SDQM [3-0]                  | AAAA         | XXAA          | ХХАА          | XXXA            | ХХХА            | ХХХА            | XXXA            |  |  |

| Bit Number<br>XD            | 31 0<br>ABCD | 15 0<br>CD    | 15 0<br>AB    | 7 0<br>D        | 7 0<br>C        | 7 0<br>B        | 7 0<br>A        |  |  |

| Bit Number<br>Ext. Mem Data | 31 0<br>ABCD | 15 0<br>CD    |               |                 | 7 0<br>C        | 7 0<br>B        | 7 0<br>A        |  |  |

| Timing Sequence             |              | 1st read      | 2nd read      | 1st read        | 2nd read        | 3rd read        | 4th read        |  |  |

Table 4.2-6 Word access read operation with Little Endian

Using little-endian and half-word access, Program/Data path between register and external memory. HA = Address whose LSB is 0,2,4,6,8,A,C,E HAL = Address whose LSB is 0,4,8,C HAU = Address whose LSB is 2,6,A,E X = Don't carenWBE [3-0] / SDQM [3-0] = A means active and U means inactive

| Access Operation | Write | e Operation (C | CPU Register 🗲 External Memory) |      |  |  |  |  |

|------------------|-------|----------------|---------------------------------|------|--|--|--|--|

| XD Width         | Wo    | ord            | Half Word                       | Byte |  |  |  |  |

| Bit Number       | 31    | 0              | 31 0                            | 31 0 |  |  |  |  |

| CPU Reg Data     | AB    | CD             | ABCD                            | ABCD |  |  |  |  |

| SA               | HAL   | HAU            | HA                              | НА   |  |  |  |  |

| Bit Number                 | 31 0  | 31 0  | 31 0  | 31 0      | 31 0      |

|----------------------------|-------|-------|-------|-----------|-----------|

| SD                         | CD CD | CD CD | CD CD | CD CD     | CD CD     |

| Bit Number                 | 31 0  | 31 0  | 31 0  | 7 0       | 7 0       |

| ED                         | CD CD | CD CD | CD CD | D         | С         |

| ХА                         | HAL   | HAL   | НА    | НА        | HA+1      |

| nWBE [3-0] /<br>SDQM [3-0] | UUAA  | AAUU  | ХХАА  | XXXA      | XXXA      |

| Bit Number                 | 31 0  | 31 0  | 15 0  | 7 0       | 7 0       |

| XD                         | CD CD | CD CD | CD    | D         | С         |

| Bit Number                 | 15 0  | 31 16 | 15 0  | 7 0       | 7 0       |

| Ext. Mem Data              | CD    | CD    | CD    | D         | С         |

| Timing Sequence            |       |       |       | 1st write | 2nd write |

Table 4.2-7

Half-word access write operation with Little Endian

| Access Operation | Read  | l Operation (C | PU Register 🗲 | External Mem | nory)    |

|------------------|-------|----------------|---------------|--------------|----------|

| XD Width         | Word  |                | Half Word     | Byte         |          |

| Bit Number       | 15 0  | 15 0           | 15 0          | 15           | 0        |

| CPU Reg Data     | CD    | AB             | CD            | С            | D        |

| SA               | HAL   | HAU            | НА            | Н            | A        |

| Bit Number       | 15 0  | 15 0           | 15 0          | 15           | 0        |

| SD               | CD    | AB             | CD            | CD           |          |

| Bit Number       | 15 0  | 15 0           | 15 0          | 15 0         | 15 0     |

| ED               | CD    | AB             | CD            | XD           | CD       |

| ХА               | HAL   | HAL            | НА            | НА           | HA+1     |

| SDQM [3-0]       | UUAA  | AAUU           | ХХАА          | XXXA         | XXXA     |

| Bit Number       | 31 0  | 31 0           | 15 0          | 7 0          | 7 0      |

| XD               | AB CD | AB CD          | CD            | D            | С        |

| Bit Number       | 31 0  |                | 15 0          | 7 0          | 7 0      |

| Ext. Mem Data    | ABCD  |                | CD            | D            | С        |

| Timing Sequence  |       |                |               | 1st read     | 2nd read |

Table 4.2-8 Half-word access read operation with Little Endian

Using little-endian and byte access, Program/Data path between register and external memory. BA = Address whose LSB is 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F

BAL = Address whose LSB is 0,2,4,6,8,A,C,E BAU = Address whose LSB is 1,3,5,7,9,B,D,F

BA0 = Address whose LSB is 0,4,8,C BA1 = Address whose LSB is 1,5,9,D

BA2 = Address whose LSB is 2,6,A,E BA3 = Address whose LSB is 3,7,B,F

| Access Operation |                 | Write Operation (CPU Register -> External Memory) |  |  |     |      |      |  |

|------------------|-----------------|---------------------------------------------------|--|--|-----|------|------|--|

| XD Width         |                 | Word                                              |  |  |     | Word | Byte |  |

| Bit Number       |                 | 31 0                                              |  |  |     | 31 0 |      |  |

| CPU Reg Data     |                 | ABCD                                              |  |  |     | ABCD |      |  |

| SA               | BAO BA1 BA2 BA3 |                                                   |  |  | BAL | BAU  | ВА   |  |

| Bit Number<br>SD           | 31 0<br>D D D D |

|----------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Bit Number<br>ED           | 7 0<br>D        | 15 8<br>D       | 23 16<br>D      | 31 24<br>D      | 7 0<br>D        | 15 8<br>D       | 7 0<br>D        |

| ХА                         | BAO             | BAO             | BAO             | BAO             | BAL             | BAL             | BA              |

| nWBE [3-0] /<br>SDQM [3-0] | UUUA            | UUAU            | UAUU            | AUUU            | XXUA            | XXAU            | ХХХА            |

| Bit Number                 | 31 0            | 31 0            | 31 0            | 31 0            | 15 0            | 15 0            | 7 0             |

| XD                         | XXXD            | XXDX            | X D X X         | DXXX            | X D             | DX              | D               |

| Bit Number                 | 7 0             | 15 8            | 23 16           | 31 24           | 7 0             | 15 8            | 7 0             |

| Ext. Mem Data              | D               | D               | D               | D               | D               | D               | D               |

| Timing Sequence            |                 |                 |                 |                 |                 |                 |                 |

Table 4.2-9

Byte access write operation with Little Endian

| Access Operation |      | Read Operation (CPU Register 🗲 External Memory) |      |      |      |      |      |  |  |

|------------------|------|-------------------------------------------------|------|------|------|------|------|--|--|

| XD Width         |      | Wo                                              | ord  | Half | Byte |      |      |  |  |

| Bit Number       | 7 0  | 7 0                                             | 7 0  | 7 0  | 7 0  | 7 0  | 7 0  |  |  |

| CPU Reg Data     | D    | С                                               | В    | А    | D    | С    | D    |  |  |

| SA               | BAO  | BA1                                             | BA2  | BA3  | BAL  | BAU  | BA   |  |  |

| Bit Number       | 7 0  | 7 0                                             | 7 0  | 7 0  | 7 0  | 7 0  | 7 0  |  |  |

| SD               | D    | С                                               | В    | А    | D    | С    | D    |  |  |

| Bit Number       | 7 0  | 7 0                                             | 7 0  | 7 0  | 7 0  | 7 0  | 7 0  |  |  |

| ED               | D    | С                                               | В    | А    | D    | С    | D    |  |  |

| ХА               | BAO  | BAO                                             | BAO  | BAO  | BAL  | BAL  | BA   |  |  |

| SDQM [3-0]       | UUUA | UUAU                                            | UAUU | AUUU | XXUA | XXAU | XXXA |  |  |

| Bit Number       | 31 0 | 31 0                                            | 31 0 | 31 0 | 15 0 | 15 0 | 7 0  |  |  |

| XD               | ABCD | ABCD                                            | ABCD | ABCD | CD   | CD   | D    |  |  |

| Bit Number       |      | 31                                              | 0    | 15   | 0    | 7 0  |      |  |  |

| Ext. Mem Data    |      | AB                                              | CD   | С    | D    | D    |      |  |  |

| Timing Sequence  |      |                                                 |      |      |      |      |      |  |  |

Table 4.2-10

Byte access read operation with Little Endian

#### 4.2.5 Bus Arbitration

The W55VA91's internal function blocks or external devices can request mastership of the system bus and then hold the system bus in order to perform data transfers. Because the design of W55VA91 bus allows only one bus master at a time, a bus controller is required to arbitrate when two or more internal units simultaneously request bus mastership. When bus mastership is granted to an internal function block, other pending requests are not acknowledged until the previous bus master has released the bus.

W55VA91 supports two priority modes, the **Fixed Priority Mode** and the **Rotate Priority Mode**, depends on the **PRTMOD** bit setting.

#### 4.2.5.1 Fixed Priority Mode

In **Fixed Priority Mode** (**PRTMOD**=0, default value), to facilitate bus arbitration, priorities are assigned to each internal W55VA91 function block. The bus controller arbitration requests for the bus mastership according to these fixed priorities. In the event of contention, mastership is granted to the function block with the highest assigned priority. These priorities are listed in **Table 4.2-11**.

| Bus<br>Priority | Function Block |

|-----------------|----------------|

| 1 (Highest)     | Video IN       |

| 2               | VPOST          |

| 3               | JPEG           |

| 4               | GPU            |

| 5               | 2-D GE (debug) |

| 6               | VRAM Loader    |

| 7               | USB Host       |

| 8               | SD Card Host   |

| 9               | Audio DAC DMA  |

| 10              | General DMA0   |

| 11              | General DMA1   |

| 12(Lowest)      | ARM Core       |

Table 4.2-11 Bus Priorities for Arbitration in Fixed Priority Mode

#### 4.2.5.2 Rotate Priority Mode

In **Rotate Priority Mode (PRTMOD**=1), W55VA91 uses a round robin arbitration scheme ensures that all bus masters have equal chance to gain the bus and that a retracted master does not lock up the bus.

#### 4.2.6 Power Management

W55VA91 provide three power management scenarios to reduce power consumption. The peripherals' clocks can be enabled or disabled individually by controlling the corresponding bit in CLKSEL control register. Software can turn-off the unused modules' clocks to saving the unnecessary power consumption.

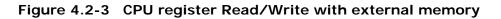

#### IDLE Mode

If the IDLE bit in Power Management Control Register (PMCON) is set, the ARM CORE clock source will be halted, the ARM CORE will not go forward. The AHB or APB clocks still active except the clock to ARM9 core are stopped. W55VA91 will exit idle state when nIRQ or nFIQ from any peripheral is received; like keypad, timer overflow interrupts and so on. The memory controller can also be forced to enter idle state if both MIDLE and IDLE bits are set. Software must switch SDRAM into self-refresh mode before force memory enter idle mode.

Figure 4.2-5 Power Management – Clock Control, Case 2

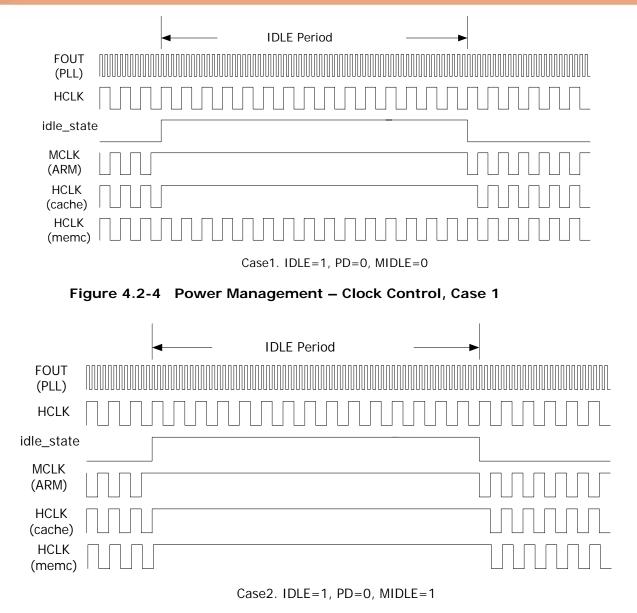

#### Power-Down Mode

The mode provides the minimum power consumption. When the W55VA91 system is not working or waiting an external event, software can write PD bit "1" to turn off all the clocks includes system crystal oscillator to let ARM CORE enter sleep mode. In this state, all peripherals are also in sleep mode since the clock source is stopped. W55VA91 will exit power down state when nIRQ/nFIQ is detected. W55VA91 provides external interrupt nIRQ[3:0], and Low-Voltage-Detector to wakeup the system clock. In addition, a Low-Voltage-Reset will also wakeup the system clock and activate a reset condition.

Figure 4.2-6 Power Management – Clock Control, Case 3

### 4.2.7 Power-On Setting

After power on reset, there are four Power-On setting pins to configure W55VA91 system configuration.

| Power-On Setting                           | Pin        |

|--------------------------------------------|------------|

| Internal PLL-generated System Clock Select | MA18       |

| Internal Boot ROM Select                   | MA16       |

| Boot ROM/FLASH Data Bus Width              | MA [15:14] |

Table 4.2-12

Power-On Setting and Description

#### MA18 pin : Internal PLL-generated System Clock Select

If pin MA18 is pull-down, the external clock from EXTAL pin is served as internal system clock. If pin MA18 is pull-up, the PLL output clock is used as internal system clock.

#### MA16 pin: Internal Boot ROM Select

If pin MA16 is pull-down, the external ROM/Flash bank connected on EBI bus is served as Booting-up program source rather than the program code contained in the internal Boot ROM.

If pin MA16 is pull-up, the Booting-up program code contained in the internal Boot ROM is the one boots and setups the whole system.

#### MA [15:14] : Boot ROM/FLASH Data Bus Width

| MA[1      | 5:14]     | Bus Width |

|-----------|-----------|-----------|

| Pull-down | Pull-down | 8-bit     |

| Pull-down | Pull-up   | 16-bit    |

| Pull-up   | Pull-down | 32-bit    |

| Pull-up   | Pull-up   | RESERVED  |

#### MA[13:8]: Power On Setting Value for Software Reference

These setting values are for software in boot ROM, especially for internal boot ROM, to detect as a reference for its own configuration usages.

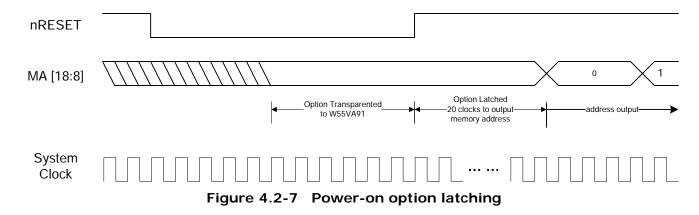

**NOTE:** Power on setting values are transparent to W55VA91 through these address pins when pin "nRESET" is LOW. And they are latched and fixed after "nRESET" going high. After "nRESET" going high, the address pins will function as memory address pins. Following plot illustrates the power-on option latching process.

#### MA[21:19] : Test Mode Configuration at Power On

Power-on setting, from A[21:19] address pins of EBI (External Bus Interface), configures the W55VA91 pins to three test modes, **(1) CPU Core test (2) Internal SRAM test (3) DFT test mode**. The test mode enable pin "TEST" should also be always set HIGH.

| TEST              | MCKE | MA[21] | MA[20:19] | Configuration<br>Mode | Description                                  |  |  |  |

|-------------------|------|--------|-----------|-----------------------|----------------------------------------------|--|--|--|

| 1                 | 1    | х      | xx        | DFT test mode         | Reserved for Design Testability              |  |  |  |

| 1                 | 0    | 0      | 00        | CPU Core Test         | ARM9 test chip                               |  |  |  |

| 1                 | 0    | 0      | 01        | Internal SRAM Test    | Internal SRAM memory test                    |  |  |  |

| 1                 | 0    | 1      | 00        | Analog Test Mode 1    | Test Audio DAC and TV DAC                    |  |  |  |

| 1                 | 0    | 1      | 01        | Analog Test Mode 2    | Test AD Converter, Touch Panel and LVD / LVR |  |  |  |

| 0                 | х    | х      | xx        | Normal Run Mode       | W55VA91 run in normal operating              |  |  |  |

| Note:<br>1. All N |      |        |           |                       |                                              |  |  |  |

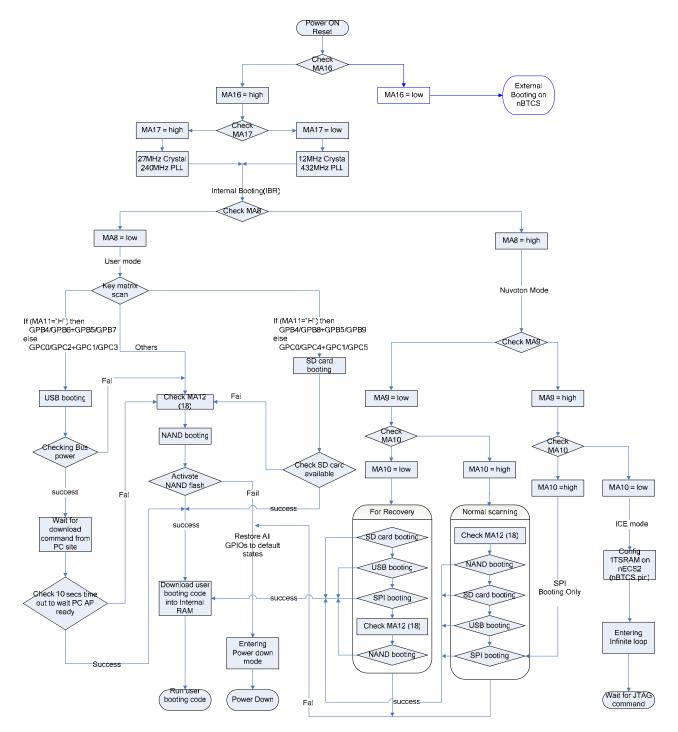

### 4.2.8 Internal Boot ROM Flow Chart

The Boot program combine different programs allowing download and/or upload into the internal memories of the chip. It implements the algorithm shown in Figure 4.2.8.

#### Figure 4.2-8 Internal Booting flow chart

#### There are some matters needing attentions:

- 1. If use SD or NAND booting, the system need a SDRAM to act as the bridge.

- 2. Can support SPI flash.

- 3. For Standard NAND Flash, load 8K(16 pages) on block 0 into internal RAM

- 4. For Advanced NAND Flash, load 16K(8 pages) on block 0 into internal RAM

- 5. User booting code on internal starting address is fixed to 0xFFE76000

- 6. Whenever booting fail on any devices, TV will show hint messages then boot next devices

- 7. SD card booting will occupy GPA1~GPA6 IO pins

### **Confidential**

- 8. When entering infinite loop, the ICE still can connect and download program

- 9. NAND booting also supports OTP (One-Time-Programmable) NAND type flash.

- 10. For SD card booting, IBR also load 16K bytes user booting code into internal RAM

- 11. For Nuvoton mode NAND flash recovery, MA9 = low and MA10 = low will entering recovery mode

- 12. Internal Booting ROM will be remapped to 0x60000000

- 13. If MA11=High ,It will be set GPB4 and GPB5 as input pin and GPB6, GPB7, GPB8, GPB9 as output pin (User Mode) ,If MA11=Low ,It will be set GPC0 and GPC1 as input pin and GPC2, GPC3, GPC4, GPC5 as output pin .

- 14. Once VA91 connected to PC, if AP on PC site is not activated or connected in 10secs with user mode and 20secs with Nuvoton mode. The time out occurs and switches booting path to NAND booting.

- 15. Before entering to power down, all the IPs and GPIO will be reset to their default states.

- 16. GPD0 is used for SDC power control. If booting success from SDC, it will be keep to GPIO function on address bus. But booting fail form SDC, it will be switch to address bus function.

- 17. 16 bit 1T-SRAM module must be connected to external IO bank 2 on nBTCS pin.

- 18. NAND flash must be connected with virtual NAND interface. The GPA11 is used for ready/busy status pin, GPA12 for Output enable, GPA13 for write enable, GPA10 for CLE pin and GPA9 for ALE pin.

- 19. If MA12 setting to "H", It will be NAND booting from MD24 ~ MD31 data bus. But MA12 setting to "L", It will be NAND booting from GPB3 ~ GPB10 data bus, If choose it function, User mode can not use GPB key matrix mode, only use GPC key matrix mode.

| Register     | Address      | R/W | Description                                       | Reset Value |

|--------------|--------------|-----|---------------------------------------------------|-------------|

| SYS_BA = 0xF | FF0_0000     |     |                                                   |             |

| PDID         | SYS_BA+0x000 | R   | Product Identifier Register                       | 0xXX55_0091 |

| PWRON        | SYS_BA+0x004 | R/W | Power-On Configurations from EBI Address          | 0x0000_0XXX |

| ARBCON       | SYS_BA+0x008 | R/W | Arbitration Control Register                      | 0x0000_0000 |

| PLLCON       | SYS_BA+0x00C | R/W | PLL Control Register                              | 0x0000_4F27 |

| CLKMAN       | SYS_BA+0x010 | R/W | Clock source Management for peripherals           | 0x0016_EC48 |

| CLKSEL       | SYS_BA+0x014 | R/W | Clock Source Select and Division setting Register | 0x0011_45FF |

| RSTCON       | SYS_BA+0x018 | W   | Reset Control Register                            | 0x0000_0000 |

| PINFUN       | SYS_BA+0x01C | R/W | Pins Multifunction Control Register               | 0x0000_0000 |

| XTLCON       | SYS_BA+0x020 | R/W | Crystal on/off status Control Register            | 0x0000_0009 |

| IRQWAKECON   | SYS_BA+0x024 | R/W | IRQ Wakeup Control register                       | 0x0000_0000 |

| IRQWAKEFLAG  | SYS_BA+0x028 | R/W | IRQ wakeup Flag Register                          | 0x0000_0000 |

| PMCON        | SYS_BA+0x02C | R/W | Power Manager Control Register                    | 0x0000_0000 |

| GPABDS       | SYS_BA+0x030 | R/W | GPA/B dual driving output selection               | 0x0000_0000 |

| GPCEDS       | SYS_BA+0x034 | R/W | GPC/E dual driving output selection               | 0x0000_0000 |

#### 4.2.9 System Manager Control Registers

| EBIDS   | SYS_BA+0x038 | R/W | EBI triple driving output selection                    | 0x0000_00AA |

|---------|--------------|-----|--------------------------------------------------------|-------------|

| SYSDIV  | SYS_BA+0x03C | R/W | System clock divider Register                          | 0x0000_1111 |

| IBTBAS  | SYS_BA+0x040 | R/W | Internal Boot ROM Base                                 | 0x0000_0000 |

| WMAPO   | SYS_BA+0x044 | R/W | Working (or Video) RAM mapping to start address<br>0x0 | 0x0000_0000 |

| PINFUN2 | SYS_BA+0x048 | R/W | Pins Multifunction 2 Control Register                  | 0x0000_0000 |

| RAMBIST | SYS_BA+0x050 | R/W | CPU RAM BIST Control Register                          | 0x0000_0000 |

| RAMSTAT | SYS_BA+0x054 | R   | CPU RAM BIST Status Register                           | 0x0000_0000 |

### Product Identifier Register (PDID)

This register is for only read and enables software to recognize certain characteristics of the chip ID and the version number.

| Register | Address      | R/W | Description                 | Reset Value |

|----------|--------------|-----|-----------------------------|-------------|

| PDID     | SYS_BA+0x000 | R   | Product Identifier Register | 0xXX55_0091 |

| 31 | 30               | 29 | 28  | 27  | 26 | 25 | 24 |  |  |  |

|----|------------------|----|-----|-----|----|----|----|--|--|--|

|    | RESERVED VERSION |    |     |     |    |    |    |  |  |  |

| 23 | 22               | 21 | 20  | 19  | 18 | 17 | 16 |  |  |  |

|    |                  |    | CHI | PID |    |    |    |  |  |  |

| 15 | 14               | 13 | 12  | 11  | 10 | 9  | 8  |  |  |  |

|    |                  |    | СНІ | PID |    |    |    |  |  |  |

| 7  | 7 6 5 4 3 2 1 0  |    |     |     |    |    |    |  |  |  |

|    | CHPID            |    |     |     |    |    |    |  |  |  |

| Bits    | Descriptions |                                                                | Default  |

|---------|--------------|----------------------------------------------------------------|----------|

| [29:24] | VERSION      | Version of the chip.                                           |          |

| [23:0]  | CHPID        | Chip identifier<br>The chip identifier of W55VA91 is 0x550091. | 0x550091 |

### Power-On Configuration from EBI Address (PWRON)

| Register | Address      | -   | •                                                        | Reset Value |

|----------|--------------|-----|----------------------------------------------------------|-------------|

| PWRON    | SYS_BA+0x004 | R/W | Power-On Configuration and Alternate<br>Setting Register | 0x0000_0XXX |

| 31 | 30                      | 29 | 28   | 27   | 26 | 25 | 24 |  |  |

|----|-------------------------|----|------|------|----|----|----|--|--|

|    | RESERVED                |    |      |      |    |    |    |  |  |

| 23 | 22                      | 21 | 20   | 19   | 18 | 17 | 16 |  |  |

|    |                         |    | RESE | RVED |    |    |    |  |  |

| 15 | 14                      | 13 | 12   | 11   | 10 | 9  | 8  |  |  |

|    | RESERVED IPLLS RESERVED |    |      |      |    |    |    |  |  |

ηυνοΤοη

| 7   | 6    | 5 | 4 | 3 | 2     | 1 | 0 |

|-----|------|---|---|---|-------|---|---|

| EBT | SIZE |   |   |   | SWREF |   |   |

| Bits  | Descriptions |                                                                                                                                                                                                                                                                                                                                              |

|-------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [10]  | IPLLS        | <ul> <li>Internal PLL-generated clock Selection</li> <li>0 = External Crystal oscillator clock is the main system clock source</li> <li>1 = Internal PLL-generated clock is selected as the main system clock source</li> <li>NOTE: This bit has a initial setting at power-on from EBI MA[18] and can be alternated by software.</li> </ul> |

| [8]   | IBTS         | <ul> <li>Internal Boot ROM Selected</li> <li>0 = External Boot ROM is selected as boot ROM device.</li> <li>1 = Internal Boot ROM is selected as boot ROM device.</li> <li>NOTE: This bit has a initial setting at power-on from EBI MA[16] and can be alternated by software.</li> </ul>                                                    |

| [7:6] | EBTSIZE      | External Boot ROM BIT width Size<br>00 = External Boot ROM is 8-bit width<br>01 = External Boot ROM is 16-bit width<br>10 = External Boot ROM is 32-bit width<br>11 = Reserved<br>NOTE: These bit have a initial setting at power-on from EBI MA[15:14] and can<br>be alternated by software.                                                |

| [5:0] | PWR_SWREF    | <b>Power-On values for SoftWare Reference</b><br>The value of these bits are from EBI MA[13:8] at power-on. Any value in these<br>bits would not affect any hardware behavior but software can access it to be a<br>decision reference. All or some of these bits can be "don't care" values if<br>software doesn't use them as references.  |

### Arbitration Control Register (ARBCON)

| Register | Address     | R/W    | Descr                                 | Description Reset Value |    |    |    |  |  |

|----------|-------------|--------|---------------------------------------|-------------------------|----|----|----|--|--|

| ARBCON   | SYS_BA+0x00 | 08 R/W | Arbitration Control Register 0x0000_0 |                         |    |    |    |  |  |

|          |             |        |                                       |                         |    |    |    |  |  |

| 31       | 30          | 29     | 28                                    | 27                      | 26 | 25 | 24 |  |  |

|          |             |        | RESI                                  | ERVED                   |    |    |    |  |  |

| 23       | 22          | 21     | 20                                    | 19                      | 18 | 17 | 16 |  |  |

|          | RESERVED    |        |                                       |                         |    |    |    |  |  |

| 15       | 14       | 13 | 12 | 11    | 10   | 9       | 8       |  |

|----------|----------|----|----|-------|------|---------|---------|--|

|          | RESERVED |    |    |       |      |         |         |  |

| 7        | 6        | 5  | 4  | 3     | 2    | 1       | 0       |  |

| RESERVED |          |    |    | IPACT | IPEN | PRTMOD1 | PRTMODO |  |

| Bits | Descriptions |                                                                                                                                 | Default |

|------|--------------|---------------------------------------------------------------------------------------------------------------------------------|---------|

| [3]  | IPACT        | Interrupt priority active (Read only)<br>When IPEN="1", this bit is set when the ARM core has an unmasked<br>interrupt request. | 0x0     |

| [2] | This bit is available only when the PRTMOD0=0. |                                                                                                                                  | 0x0 |

|-----|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|

| [1] | PRTMOD1                                        | <ul> <li>PRTMOD1: AHB2 Master Priority mode select</li> <li>0 = Fixed Priority Mode</li> <li>1 = Rotate Priority Mode</li> </ul> | 0x0 |

| [0] | PRTMODO                                        | AHB1 Master Priority mode select<br>0 = Fixed Priority Mode<br>1 = Rotate Priority Mode                                          | 0x0 |

### PLL Control Register (PLLCON)

| Register | Address     | R/W   | Descri   | Description Reset V |    |     |           |  |  |

|----------|-------------|-------|----------|---------------------|----|-----|-----------|--|--|

| PLLCON   | SYS_BA+0x00 | C R/W | PLL Co   | ntrol Register      |    | 0x0 | 0000_4F27 |  |  |

|          |             |       |          |                     |    |     |           |  |  |

| 31       | 30          | 29    | 28       | 27                  | 26 | 25  | 24        |  |  |

|          |             |       | RESE     | RVED                |    |     |           |  |  |

| 23       | 22          | 21    | 20       | 19                  | 18 | 17  | 16        |  |  |

|          |             |       | RESERVED |                     |    |     | PWDEN     |  |  |

| 15       | 14          | 13    | 12       | 11                  | 10 | 9   | 8         |  |  |

| FBDV     |             |       |          |                     |    |     |           |  |  |

| 7        | 6           | 5     | 4        | 3                   | 2  | 1   | 0         |  |  |

| FBDV     | ΟΤΙ         | DV    |          | INDV                |    |     |           |  |  |

| Bits   | Descriptions |                                                                                                    |                                                                                                                                                                                                                                                                              |  |  | Default |  |  |

|--------|--------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|---------|--|--|

| [16]   | PWDEN        | 0 = PLL is in no<br>1 = PLL is in por<br><b>NOTE:</b> If power<br>default of this                  | <ul> <li>Power down mode enable</li> <li>0 = PLL is in normal mode</li> <li>1 = PLL is in power down mode</li> <li>NOTE: If power-on setting of MA18 (IPLLS) is '0'. The default of this bit will be '1', PLL is power-down.</li> <li>Otherwise, this bit is '0'.</li> </ul> |  |  |         |  |  |

| [15:7] | FBDV         | •                                                                                                  | PLL VCO output clock feedback divider<br>Feedback Divider divides the output clock from VCO of PLL.                                                                                                                                                                          |  |  |         |  |  |

| [6:5]  | οτον         | OTDV [6:5]           0         0           0         1           1         0           1         1 | Ox1                                                                                                                                                                                                                                                                          |  |  |         |  |  |

| [4:0]  | INDV         | PLL input cloc<br>Input Divider d                                                                  | 0x7                                                                                                                                                                                                                                                                          |  |  |         |  |  |

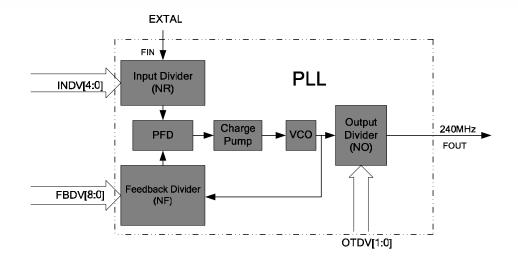

The formula of output clock of PLL is:

FOUT = FIN  $*\frac{NF}{NR}*\frac{1}{NO}$

FOUT : Output clock of Output Divider FIN : External clock into the Input Divider NR : Input divider value (NR = INDV + 2) NF : Feedback divider value (NF = FBDV + 2) NO : Output divider value (NO = OTDV)

#### **Clock Source Management for Peripherals (CLKMAN)**

| Register | Address    | R/W      | Desc    | ription                                                | Re       | Reset Value  |             |  |

|----------|------------|----------|---------|--------------------------------------------------------|----------|--------------|-------------|--|

| CLKMAN   | SYS_BA+0x0 | 010 R/W  |         | Clock source enable/disable management for peripherals |          | nagement 0x0 | 0x0016_EC48 |  |

| -        |            |          |         |                                                        |          |              | -           |  |

| 31       | 30         | 29       | 28      | 27                                                     | 26       | 25           | 24          |  |

|          |            |          | RES     | ERVED                                                  |          |              |             |  |

| 23       | 22         | 21       | 20      | 19                                                     | 18       | 17           | 16          |  |

| RESERVED |            | I2CCK_EN | UHC_EN  | USB48_EN                                               | USBCK_EN | RESERVED     |             |  |

| 15       | 14         | 13       | 12      | 11                                                     | 10       | 9            | 8           |  |

| WDT_EN   | TMR_EN     | PWM_EN   | SPI_EN  | UART_EN                                                | ADC_EN   | GDMA_EN      | GPU_EN      |  |

| 7        | 6          | 5        | 4       | 3                                                      | 2        | 1            | 0           |  |

| GE EN    | VPST EN    | VID EN   | JPEG EN | SDH EN                                                 | AUD EN   | RESE         | RVED        |  |

| Bits | Descriptions |                                                                                                                                               | Default |

|------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------|

| [20] | I 2CCK_EN    | <ul> <li>12C operation and driving clock enable bit</li> <li>0 = 12C operation is disabled.</li> <li>1 = 12C operation is enabled.</li> </ul> | 0x1     |

|      | 1        |                                                                                                                                                                                                                                                                                                                                                              |     |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| [19] | UHC_EN   | <ul> <li>USB Host Controller clock enable bit</li> <li>0 = USB Host Controller operation is disabled.</li> <li>1 = USB Host Controller operation is enabled.</li> </ul>                                                                                                                                                                                      | 0x0 |

| [18] | USB48_EN | <ul> <li>USB driving clock for 48MHz enable bit</li> <li>0 = USB 48MHz driving clock is disabled.</li> <li>1 = USB 48MHz driving clock is enabled.</li> </ul>                                                                                                                                                                                                | 0x1 |

| [17] | USBCK_EN | <ul> <li>USB operation and driving clock enable bit</li> <li>0 = USB operation is disabled. Driving clock to USB is also disabled.</li> <li>1 = USB operation and driving clock are enabled.</li> </ul>                                                                                                                                                      | 0x1 |

| [15] | WDT_EN   | <ul> <li>WDT driving clock enable bit</li> <li>0 = WDT driving clock disabled.</li> <li>1 = WDT driving clock enabled, setting to WDT and WDT operation is effective.</li> </ul>                                                                                                                                                                             | 0x1 |

| [14] | TMR_EN   | <ul> <li>Timer operation and driving clock enable bit</li> <li>0 = Timer operation is disabled. Driving clock to timer is also disabled.</li> <li>1 = Timer operation and driving clock are enabled.</li> </ul>                                                                                                                                              | 0x1 |

| [13] | PWM_EN   | <ul> <li>PWM operation and driving clock enable bit</li> <li>0 = PWM operation is disabled. Driving clock to PWM is also disabled.</li> <li>1 = PWM operation and driving clock are enabled.</li> </ul>                                                                                                                                                      | 0x1 |

| [12] | SPI_EN   | <ul> <li>SPI operation and driving clock enable bit</li> <li>0 = SPI operation is disabled. Driving clock to SPI is also disabled.</li> <li>1 = SPI operation and driving clock are enabled.</li> </ul>                                                                                                                                                      | 0x0 |

| [11] | UART_EN  | <ul> <li>UART operation and driving clock enable bit</li> <li>0 = UART operation is disabled. Driving clock to UART is also disabled.</li> <li>1 = UART operation and driving clock are enabled.</li> </ul>                                                                                                                                                  | 0x1 |

| [10] | ADC_EN   | <ul> <li>ADC operation and driving clock enable bit</li> <li>0 = ADC operation and Touch-Panel operation are disabled. Driving clock to ADC and Touch-Panel modules is also disabled.</li> <li>1 = ADC and Touch-Panel operation and driving clock are enabled.</li> </ul>                                                                                   | 0x1 |

| [9]  | GDMA_EN  | <ul> <li>GDMA operation and driving clock enable bit</li> <li>0 = GDMA operation is disabled. Driving clock to GDMA is also disabled.</li> <li>1 = GDMA operation and driving clock are enabled.</li> </ul>                                                                                                                                                  | 0x0 |

| [8]  | GPU_EN   | <ul> <li>Graphic Processing Unit operation and driving clock enable bit</li> <li>0 = Graphic Processing Unit operation is disabled. Driving clock to</li> <li>Graphic Processing Unit is also disabled.</li> <li>1 = Graphic Processing Unit operation and driving clock are enabled.</li> </ul>                                                             | 0x0 |

| [7]  | GE_EN    | <ul> <li>2D Graphic Acceleration operation and driving clock enable bit</li> <li>0 = 2D Graphic Acceleration operation is disabled. Driving clock to 2D</li> <li>Graphic Acceleration is also disabled.</li> <li>1 = 2D Graphic Acceleration operation and driving clock are enabled.</li> </ul>                                                             | 0x0 |

| [6]  | VPST_EN  | <ul> <li>V-Post (Display interface) operation and driving clock enable bit</li> <li>0 = V-Post operation is disabled. Driving clock to V-Post is also disabled.</li> <li>1 = V-Post operation and driving clock are enabled.</li> <li>NOTE: V-Post (Display interface) including LCM module controller and TV-Encoder (TV-DAC included) interface</li> </ul> | Ox1 |

|     | 1      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| [5] | VID_EN | <ul> <li>Video-IN operation and driving enable clock bit</li> <li>0 = Video-in operation is disabled. Driving clock to Video-in is also disabled.</li> <li>1 = Video-in operation and driving clock are enabled.</li> <li>NOTE: Video-in interface is a image sensor interface to receive image streaming from a image sensor.</li> </ul>                                                                                                                                                                                                                | 0x0 |

| [4] | JPG_EN | <ul> <li>JPEG operation and driving clock enable bit</li> <li>0 = JPEG operation is disabled.</li> <li>1 = JPEG operation clock is enabled.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                   | 0x0 |

| [3] | SDH_EN | <ul> <li>SD Card Host Controller/DMAC operation and driving clock enable bit</li> <li>0 = SD Card Host Controller/DMAC operation is disabled. Driving clock to SD Card Host Controller/DMAC is also disabled.</li> <li>1 = SD Card Host Controller/DMAC operation and driving clock are enabled.</li> </ul>                                                                                                                                                                                                                                              | 0x1 |

| [2] | AUD_EN | <ul> <li>Audio Controller and Audio DAC operation and driving clock enable bit</li> <li>0 = Audio controller and audio DAC operation is disabled. Driving clock to Audio controller and audio DAC is also disabled.</li> <li>1 = Audio controller and audio DAC operation and driving clock are enabled.</li> <li>NOTE: Directly turn on or turn off audio DAC by toggle this bit can generate unexpected noise. To avoid that issue, please also refer to the audio DAC control part to appropriately control the audio DAC power-down bits.</li> </ul> | 0x0 |

**NOTE**: By default, all setting values of the above described bits are "1". That means all function blocks and their driving clocks are enabled after reset. Users may individually set each block enabled or disabled by their system power saving requirements.

### Clock Source Selection and Division Setting Register (CLKSEL)

| Register | Address      |     |                                                           | Reset Value |

|----------|--------------|-----|-----------------------------------------------------------|-------------|

| CLKSEL   | SYS_BA+0x014 | R/W | Clock source enable/disable management<br>for peripherals | 0x0045_17FF |

| 31        | 30        | 29       | 28       | 27        | 26       | 25       | 24       |

|-----------|-----------|----------|----------|-----------|----------|----------|----------|

| VLB_HLKEN | VPSTCKSEL | VIDCKSEL | LCDCKSEL | Reserved  | TMRCKSEL | SYS32KSL | USBCKDIV |

| 23        | 22        | 21       | 20       | 19        | 18       | 17       | 16       |

|           | USBCKDIV  |          |          | VPSTCKDIV |          |          |          |

| 15        | 14        | 13       | 12       | 11        | 10       | 9        | 8        |

|           | VIDCKI    |          |          |           |          | ADOC     | KDIV     |

| 7         | 6         | 5        | 4        | 3         | 2        | 1        | 0        |

| ADOCKDIV  |           |          |          |           |          |          |          |

| Bits    | Descriptions |                                                                                                                                                                                                                                                                                             | Default |

|---------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| [31]    | VLB_HCLKEN   | <ul> <li>VPOST Line Buffer system clock enable.</li> <li>0 = VPOST Line buffer clock source is not selected from system clock.</li> <li>1 = VPOST Line buffer clock source is selected from system clock.</li> </ul>                                                                        | 0x0     |

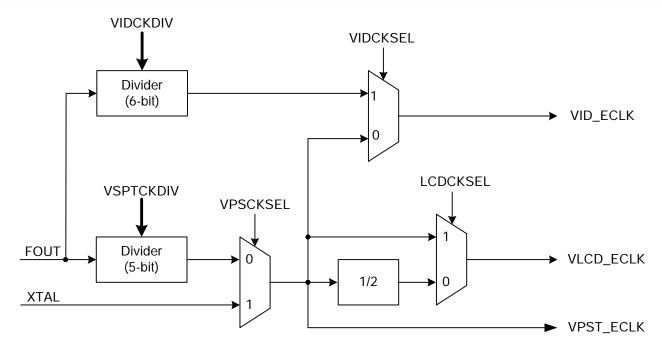

| [30]    | VPSTCKSEL    | <ul> <li>VPOST driving clock selection</li> <li>0 = Main crystal oscillator clock is selected.</li> <li>1 = Divided clock from PLL output clock (FREQ<sub>DIVOUT</sub>) is selected.</li> </ul>                                                                                             | 0x0     |

| [29]    | VIDCKSEL     | VIDEO-IN (Sensor) driving clock selection<br>0 = VPOST driving clock (27/13.5 MHz) is selected.<br>1 = Independent clock divider output is selected.                                                                                                                                        | 0x0     |

| [28]    | LCDCKSEL     | <ul> <li>VPOST(LCD) driving clock selection</li> <li>0 = VPOST (LCD) driving clock is set to 13.5MHz clock source.</li> <li>1 = VPOST (LCD) driving clock is set to 27MHz clock source.</li> </ul>                                                                                          | 0x0     |

| [26]    | TMRCKSEL     | <ul> <li>Timer driving clock source selection</li> <li>0 = Main crystal oscillator clock is selected as clock source.</li> <li>1 = 32768 crystal oscillator clock is selected as clock source.</li> </ul>                                                                                   | 0x0     |

| [25]    | SYS32KSL     | System clock selection from 32.768KHz crystal oscillator<br>0 = System clock is from divided PLL generated output or Main crystal<br>oscillator<br>1 = System clock is from 32.768KHz crystal oscillator                                                                                    | 0x0     |

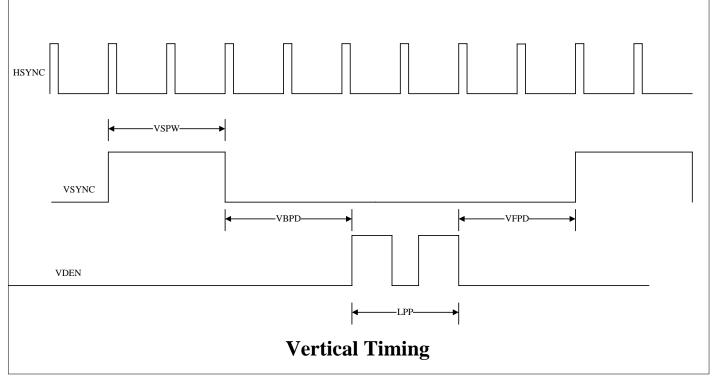

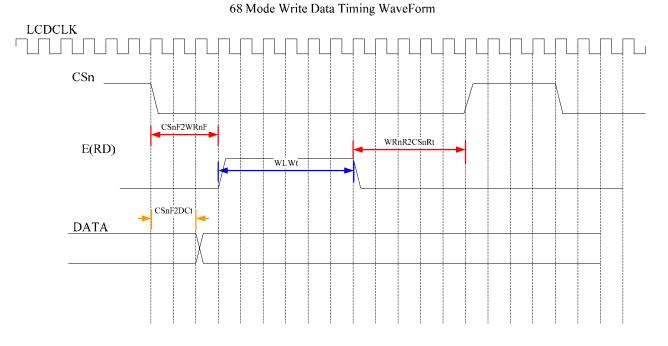

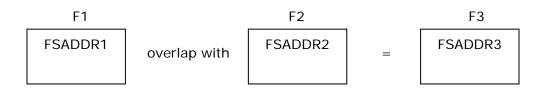

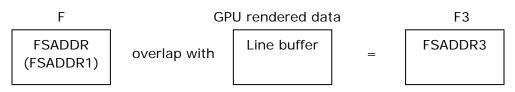

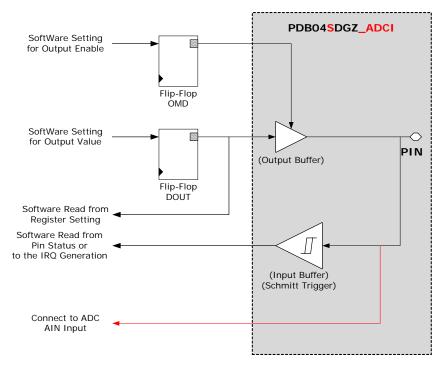

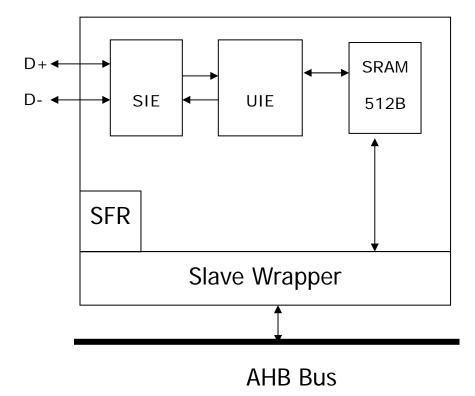

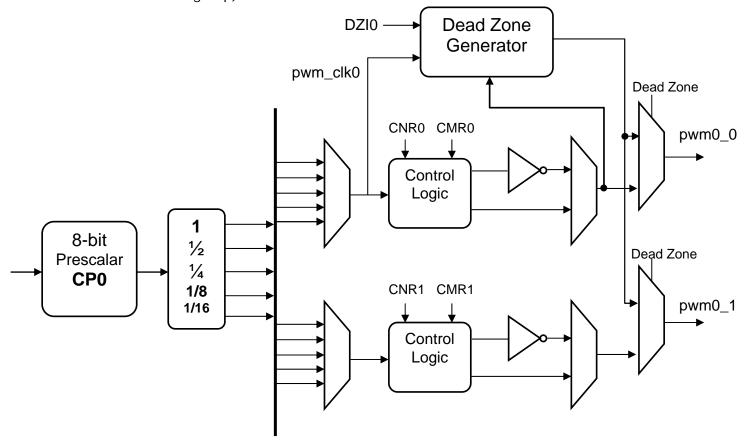

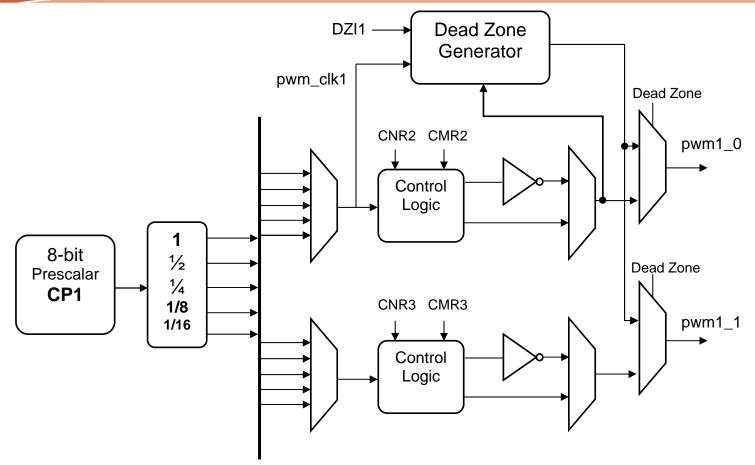

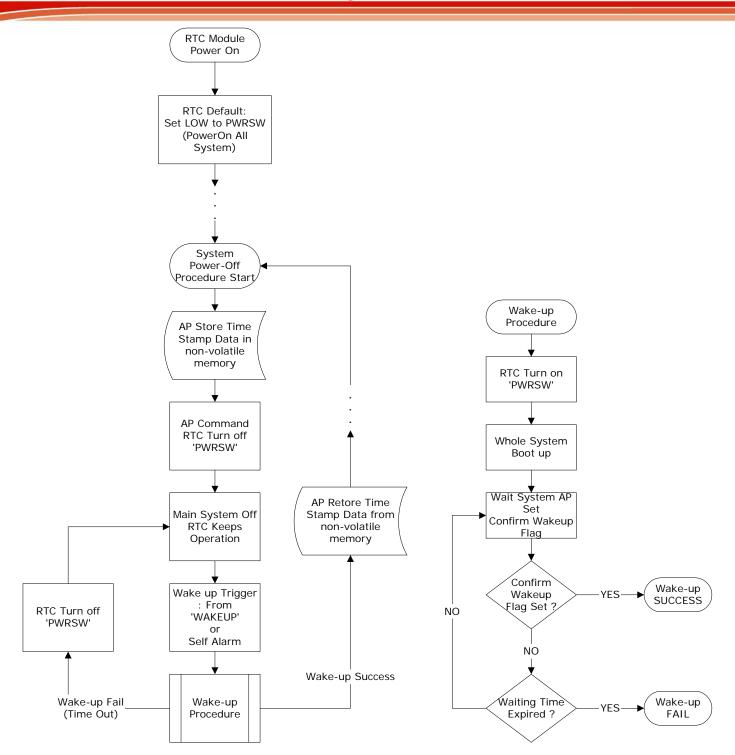

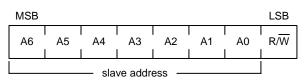

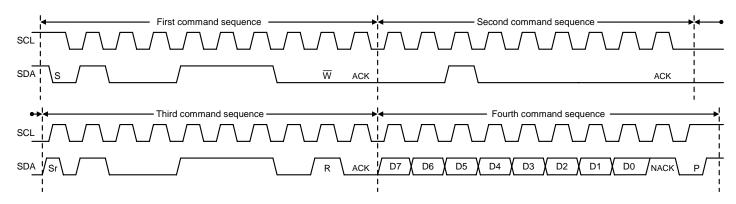

| [24:21] | USBCKDIV     | USB 48M clock source divider<br>The clock divider generate a frequency-divided clock output from<br>PLL-generated clock source for the engine clock (48MHz) of USB device<br>and Host. If N = USBCKDIV[3:0], then<br>FREQ <sub>DIVOUT</sub> = (FREQ <sub>PLL</sub> ) / (N+1).               | 0x2     |